- PICとは何ですか?

- APICとは何ですか? LAPICおよびI / O APICの目的は何ですか?

- APIC、xAPIC、およびx2APICの違いは何ですか?

- MSIとは何ですか? MSIとMSI-Xの違いは何ですか?

- テーブル$ PIR、MPtable、ACPIはこれにどのように関連していますか?

これらの質問のいずれかに対する回答を得ることに興味がある場合、または単にx86システムでの割り込みコントローラーの進化に精通したい場合は、catへようこそ。

はじめに

私たちは皆、中断が何であるかを知っています。 そうでない人のために、ウィキペディアからの引用:

割り込み(英語の割り込み)-ソフトウェアまたはハードウェアからの信号で、即時の注意が必要なイベントの発生についてプロセッサに通知します。 割り込みは、プロセッサによって実行される現在のコードの割り込みを必要とする優先度の高いイベントの発生をプロセッサに通知します。 プロセッサは、現在のアクティビティを一時停止し、状態を維持し、イベントに応答して処理する割り込みハンドラー(または割り込みハンドラー)と呼ばれる関数を実行することで応答します。その後、割り込みコードに制御を戻します。この記事では、外部IRQ割り込みについて説明します。

割り込み信号のソースに応じて、それらは次のように分類されます。

- 非同期、または外部ハードウェアデバイス(周辺機器など)から発生し、任意の瞬間に発生する可能性がある外部(ハードウェア)イベント:タイマー、ネットワークカードまたはディスクドライブからの信号、キーストローク、マウスの動き。 システムでこのような割り込みが発生したという事実は、割り込み要求(IRQ)として解釈されます。デバイスは、OSからの注意が必要であることを報告します。

- マシンコードの実行時の特定の条件の違反の結果としてのプロセッサ自体の同期または内部イベント:ゼロ除算またはスタックオーバーフロー、無効なメモリアドレスまたは無効なオペレーションコードへのアクセス。

なぜ必要なのですか? ネットワークカードが到着したときに、入力パケットを使用して何らかのアクションを実行するとします。 ネットワークカードに常に「新しいパケットがありますか?」と尋ねないようにするために、これにプロセッサリソースを無駄にしないために、IRQ割り込みを使用できます。 デバイスの割り込みラインはプロセッサのINTRラインに接続されており、パケットを受信すると、ネットワークカードはこのラインを「プル」します。 プロセッサは、それに関する情報があることを理解し、パケットを読み取ります。

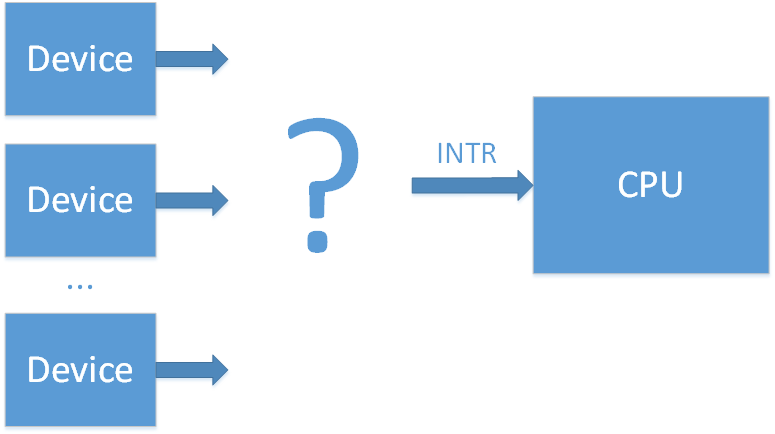

しかし、デバイスがたくさんある場合はどうでしょうか? プロセッサレッグのすべての外部デバイスを十分に入手することはできません。

この問題を解決するために、彼らはチップを思いついた-割り込みコントローラ。

写真

( wiki / osdev )

最初はIntel 8259 PICチップでした。 8つの入力ライン(IRQ0〜7)、および1つの出力がコントローラーをプロセッサーのINTRラインに接続します。 デバイスからの割り込みが発生すると、8259はINTRラインをプルし、プロセッサは一部のデバイスが割り込みを通知し、PICをポーリングしてどのIRQxレッグが割り込みを引き起こしたかを認識します。 このポーリングには追加の遅延がありますが、割り込みラインの数は8に増えます。

しかし、8行はすぐに小さくなり、その数を増やすために、カスケード接続された2つの8259コントローラー(マスターとスレーブ)を使用し始めました(デュアルPIC)。

IRQ 0〜7は最初のIntel 8259 PIC(マスター)によって処理され、IRQ 8〜15は2番目の8259 PIC(スレーブ)によって処理されます。 マスターのみが割り込みの発生を通知します。 ライン8〜15で割り込みが発生すると、2番目のPIC(スレーブ)がIRQ 2を介してマスターに割り込みを通知し、マスターがCPUに通知します。 このカスケード割り込みは、16行のうちの1つを使用しますが、最終的にはデバイスに15の使用可能な割り込みを提供します。

回路はそれ自体を確立しました、そして、これは彼らが現在PIC(Programm Interrupt Controller)について話すとき、彼らが意味することです。 その後、8259コントローラーはいくつかの改善を受け、8259Aとして知られるようになり、この回路はチップセットに組み込まれました。 外部デバイスを接続するためのメインバスがISAバスであった時代には、このようなシステム全体で十分でした。 ISA割り込みは共有されないため、競合を回避するために、異なるデバイスが同じIRQラインに接続しないようにする必要がありました。

通常、デバイスの割り込みのレイアウトは多かれ少なかれ標準でした

例( ここから引用 ):

IRQ 0-システムタイマー

IRQ 1-キーボードコントローラー

IRQ 2-カスケード(スレーブコントローラーからの割り込み)

IRQ 3-シリアルポートCOM2

IRQ 4-シリアルポートCOM1

IRQ 5-パラレルポート2および3またはサウンドカード

IRQ 6-フロッピーコントローラ

IRQ 7-パラレルポート1

IRQ 8-RTCタイマー

IRQ 9-ACPI

IRQ 10-オープン/ SCSI / NIC

IRQ 11-オープン/ SCSI / NIC

IRQ 12-マウスコントローラー

IRQ 13-数学コプロセッサー

IRQ 14-ATAチャネル1

IRQ 15-ATAチャネル2

8259超小型回路の構成と作業は、I / Oポートを介して実行されます。

| チップ | 登録する | I / Oポート |

|---|---|---|

| マスター写真 | コマンド | 0x0020 |

| マスター写真 | データ | 0x0021 |

| スレーブ写真 | コマンド | 0x00A0 |

| スレーブ写真 | データ | 0x00A1 |

→8259Aのドキュメントはこちらにあります。

ISAバスはPCIバスに置き換えられました。 デバイスの数は明らかに15を超え始めました。また、静的ISAバスとは異なり、この場合、デバイスはシステムに動的に追加できます。 しかし幸いなことに、このバスでは割り込みを共有できます(つまり、複数のデバイスを1つのIRQラインに接続できます)。 その結果、IRQラインの不足の問題を解決するために、彼らはすべてのPCIデバイスからの割り込みをPIRQライン(プログラム可能な割り込み要求)にグループ化することにしました。

PICコントローラーに4本の割り込みラインと20個のPCIデバイスがあるとしましょう。 PIRQxラインごとに5つのデバイスの割り込みを組み合わせ、PIRQxラインをコントローラーに接続します。 PIRQxラインで割り込みが発生した場合、プロセッサはこのラインに接続されているすべてのデバイスに問い合わせて、割り込みの原因を把握する必要がありますが、一般的にはこれで問題が解決します。 PIRQラインでPCI割り込みラインをバインドするデバイスは、多くの場合PIRルーターと呼ばれます。

この方法では、ISA割り込みが既に開始されているIRQxラインにPIRQxラインが接続されていないこと(競合が発生するため)、およびPIRQxラインのバランスが取れていることを確認する必要があります(同じPIRQラインに接続したデバイスが多いほど、必要なデバイスが多いため)これらのデバイスのどれが割り込みを引き起こしたかを理解するためにプロセッサに問い合わせます)。

注 :PCIデバイス-> PIRマッピングは、実際にはやや複雑であるため、要約で示されています。 実際には、各PCIデバイスには4つの割り込みライン(INTA、INTB、INTC、INTD)があります。 各PCIデバイスには最大8つの機能があり、各機能にはすでに1つのINTx割り込みがあります。 デバイスの各機能が取得するINTxの種類は、チップセットの構成によって決まります。

本質的に、関数は独立した論理ブロックです。 たとえば、1つのPCIデバイスには、Smbusコントローラー機能、SATAコントローラー機能、LPCブリッジ機能があります。 OS側から見ると、各機能は独自のPCI Config構成スペースを持つ個別のデバイスです。

BIOSは、$ PIRテーブルを使用し、各機能のPCI構成スペースの3Ch(INT_LN割り込みライン(R / W))および3Dh(INT_PN割り込みピン(RO))レジスタを埋めることにより、PIC上の割り込みルーティングに関する情報をBIOSに渡しました。 $ PIRテーブルの仕様は、以前はMicrosoftのWebサイトにありましたが、現在はありません。 $ PIRテーブルの行の内容は、 PCI BIOS仕様 [4.2.2。 PCI割り込みルーティングオプションを取得する]またはこちらをお読みください

アピック

( wiki 、 osdev )

以前の方法は、マルチプロセッサシステムが登場するまで機能しました。 実際、そのデバイスでは、PICは1つのメインプロセッサのみに割り込みを送信できます。 しかし、割り込み処理からのプロセッサの負荷のバランスを取りたいです。 この問題の解決策は、新しいインターフェイスAPIC(アドバンストPIC)でした。

各プロセッサに対して、特別なLAPICコントローラー(ローカルAPIC)が追加され、 I / O APICコントローラーがデバイスからの割り込みをルーティングするために追加されます。 これらのコントローラーはすべて、APICと呼ばれる共通バスで結合されています(新しいシステムは現在、標準システムバスを介して接続されています)。

デバイスからの割り込みがI / O APICピンに到着すると、コントローラーは割り込みをいずれかのプロセッサのLAPICにルーティングします。 I / O APICの存在により、プロセッサ間の外部デバイスからの割り込みの分散のバランスをとることができます。

最初のAPICチップは82489DXで 、LAPICとI / O APICを組み合わせた別個のチップでした。 2つのプロセッサのシステムを作成するには、3つのそのような超小型回路が必要でした。 2はLAPICとして機能し、1つはI / O APICとして機能します。 その後、LAPIC機能がプロセッサに直接組み込まれ、I / O APIC機能が82093AAチップに組み込まれました。

I / O APIC 82093AAには24個の入力ピンが含まれており、APICアーキテクチャは最大16個のCPUをサポートできます。 古いシステムとの互換性を維持するために、0〜15の割り込みが古いISA割り込みに割り当てられました。 そして、PCIデバイスからの割り込みがIRQ行16-23に表示され始めました。 これで、ISAおよびPCIデバイスからの割り込みの競合を考えないことが可能になりました。 また、空き割り込みラインの数が増えたことにより、PIRQxラインの数を増やすことも可能になりました。

I / O APICおよびLAPICプログラミングはMMIOを介して行われます。 LAPICレジスタは通常0xFEE00000にあり、I / O APICレジスタは0xFE00000にあります。 原則として、これらのアドレスはすべて再構成できます。

PICの場合のように、最初は個々のチップが後でチップセットの一部になりました。

将来、APICアーキテクチャは近代化され、新しいバージョンはxAPIC(x-拡張)と呼ばれました。 以前のバージョンとの下位互換性を保持しました。 システムで使用可能なCPUの数は256に増加しました。

アーキテクチャ開発の次のラウンドはx2APICと呼ばれていました 。 システムで使用可能なCPUの数は2 ^ 32に増加しました。 コントローラは、xAPIC互換モード、またはLAPICプログラミングがMMIOではなくMSRレジスタ(より高速)で実行される新しいx2APICモードで動作できます。 このリンクから判断すると、このモードが機能するにはIOMMUサポートが必要です。

システムには複数のI / O APICコントローラーがある場合があることに注意してください。 たとえば、1つはサウスブリッジの24の中断、もう1つは北の32の中断です。 I / Oのコンテキストでは、APIC割り込みはしばしばGSI(グローバルシステム割り込み)と呼ばれます。 そのため、このようなシステムではGSI 0-55になります。

CPUに組み込みLAPICがあり、CPUIDのビットフラグでどのアーキテクチャを理解できるか。

システムがLAPICおよびI / O APICを検出するためには、BIOSはMPtable(古い方法)またはACPIテーブル(この場合はMADT)のいずれかを介してシステムに関する情報を提供する必要があります。 一般的な情報に加えて、MPtableとACPI(今回はDSDTテーブルにあります)の両方に、割り込みルーティングに関する情報、つまりどのデバイスがどの割り込みラインにあるかに関する情報($ PIRテーブルのアナログ)を含める必要があります。

公式仕様の MPTableテーブルについて読むことができます。 以前は、仕様はインテルのWebサイトにありましたが、現在はアーカイブでのみ見つけることができます。 ACPI仕様は、現在UEFI Webサイト(現在のバージョン6.2 )にあります。 ACPIを使用すると、($ PIRテーブルを使用する代わりに)APICを使用しないシステムの割り込みルーティングを指定できることに注意してください。

Msi

( wiki )

APICを使用した以前のバージョンは良好ですが、欠陥がないわけではありません。 これらのデバイス割り込みラインはすべて、回路を複雑にし、エラーの可能性を高めます。 PCIバスはPCIエクスプレスに置き換えられ、割り込みラインは単に削除されることが決定されました。 互換性を維持するために、割り込み信号(INTx#)は特定の種類のメッセージによってエミュレートされます。 このスキームでは、以前はワイヤの物理的な接続によって行われていた割り込みラインの論理的な追加が、PCIブリッジの肩にかかっていました。 ただし、レガシーINTx割り込みサポートは、PCIバスとの下位互換性をサポートするだけです。 実際、PCIエクスプレスは、割り込みメッセージを配信する新しい方法-MSI(Message Signaled Interrupts)を提案しています。 この方法では、デバイスは割り込みを通知するために、プロセッサLAPIC用に予約されているMMIOエリアに書き込みます。

以前は、1つのPCIデバイス(つまり、そのすべての機能)に割り当てられた割り込みは4つだけでしたが、現在では最大32の割り込みに対応できるようになりました。

MSIの場合、回線の共有はなく、各割り込みはそのデバイスに対応します。

MSI割り込みは別の問題も解決します。 デバイスがメモリ書き込みトランザクションを実行し、割り込みを通じてその完了を報告したいとします。 ただし、転送プロセス中にバス上で書き込みトランザクションが遅延する可能性があり(デバイスはまったく認識しません)、割り込み信号はプロセッサの前に早く到着します。 したがって、CPUは引き続き無効なデータを読み取ります。 MSIが使用される場合、MSIに関する情報はデータと同様に送信され、単に早く来ることができません。

MSI割り込みはLAPICなしでは機能しませんが、MSIを使用するとI / O APIC(設計の簡素化)に置き換えられることに注意してください。

その後、このメソッドはMSI-X拡張を受け取りました。 これで、各デバイスは最大2048の割り込みを持つことができます。 また、実行するプロセッサ上の割り込みごとに個別に示すことが可能になりました。 これは、ネットワークカードなどの負荷の大きいデバイスに非常に役立ちます。

MSIをサポートするために追加のBIOSテーブルは必要ありません。 ただし、デバイスはPCI Configの機能の1つでMSIサポートを報告する必要があり、デバイスドライバーはMSIの操作をサポートする必要があります。

おわりに

この記事では、割り込みコントローラーの進化を調査し、x86システムの外部デバイスからの割り込みの配信に関する一般的な理論情報を受け取りました。

次のパートでは、説明した各コントローラーを実際にLinuxで使用する方法を見ていきます。