はじめに

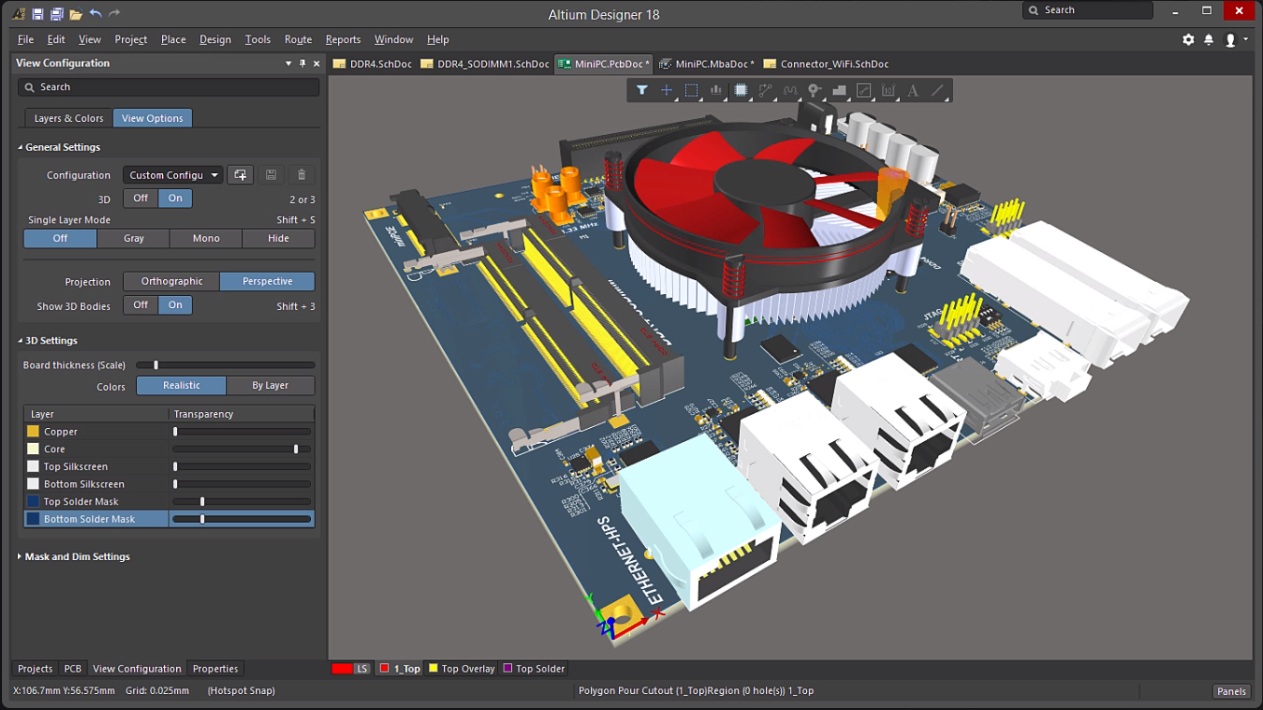

ここで、Altium Designerが何であるかを知らない人のための少しの情報を提供します。 これは、ほぼすべての複雑な電子機器を開発できる3つの人気のあるプロフェッショナルCADシステムの1つです。 残りの2つのパッケージは、Mentor Expedition(およびおそらくPADS)とAllegro Cadenceです。 これら3つのパッケージにはそれぞれ、長所と短所、および条件付き特殊化があります。 今日は比較がないので、私が自分でAltiumを選んだ理由を説明します。

- このプログラムの優れたデザインと思いやりのあるインターフェースは、単に競争を超えています。 競合他社を見るだけで、すべてが明らかになります。 はい、毎日数時間勤務している場合、デザインと使いやすさが重要です。 また、理解しやすい論理CADでの学習がはるかに簡単になるため、初心者の学習プロセスも促進されます。

- SolidWorksのような機械的な「チタン」を直接操作する機能。 ADからボードをしっかりと開き、品質を損なうことなくアセンブリの一部として追加することができます。 STEPによる変換を終了します。 私にとって、そして確かにあなたにとって、これは重要です。なぜなら、 電子デバイスは、コンポーネントを備えた単なるボードではなく、ほとんどの場合に当てはまります。 この機能により、デバイス全体のアセンブリモデルを簡単に作成し、金型の設計と製造のミスをそれぞれ3〜5千ドルで防ぐことができます。

- ロシア語で十分な量の情報が存在するため、エントリのしきい値がかなり低くなっています。 これが、AltiumがCISで優位を占める主な理由であり、他の何かではありません。 メンターまたはケイデンスがロシア語で何かを見つけようとし、すぐにそれらで働くことを学びたい。

- CISおよびアジアでは、ほとんどの企業がAltiumで働いており、米国では大きな市場シェアを持っています。 ヨーロッパでは、SolidWorks PCBが大好きです。これは、同じビルトインADです。 それは何を与えますか? エレクトロニクス開発の分野で働くことに決めた場合、あなたは簡単に仕事を見つけることができます。

はい、はい、私はあらゆる種類のシミュレーション機能、ツールなどについては話しませんでしたが、これは必要ではありません。 上記の技術的な3つのCADシステムはすべて、さまざまな程度の利便性と松葉杖を使用して、ほぼ同じことを実行できます。

Altiumでの作業方法を学びたいのですが、怖いです

かつて、2011年から2012年にかけて初めてADで働く機会がありました。 その瞬間、英語は私にとって障害であり、一般的に英語での作業方法は明確ではありませんでした。 膨大な数のツールと機能に対する私の恐怖を克服して、Comradeのビデオで助けてくれました。 Sabunina(彼に感謝)、これはロシア語でyoutubeにあり、開発の最初の一歩を踏み出すことを可能にした基本的な基本事項を説明しています。 過去6年間にロシア語でADに関する情報がさらに増えたため、エントリのしきい値がさらに低くなったため、恐れずに学習してください。

Altium Designerを習得しやすくするために、私からいくつかの「ジンジャーブレッド」を提供します。

- 一連のビデオチュートリアルはこちらです。 ビデオの長さは長いですが、基本的な機能に関する包括的な情報が含まれており(少なくとも彼らはそう言っています)、どの学生でも簡単に最初のデバイスを設計できます。

- Altium Designerのライブラリ- こちら 。 ここでは、すべての受動部品(抵抗、コンデンサなど)に加えて、MKやFPGAを含む多数の一般的なトランジスタ、ダイオード、超小型回路があります。 開始時にライブラリを作成するには時間がかかるため、時間を大幅に節約できることを願っています。

勉強の過程で質問や困難が生じた場合は、プライベートメッセージで私を書くことができます。可能であれば、全員に答えようとします。

プロジェクトが複雑になるのはいつですか?

プログラムのソースコードであれ、電子デバイスの回路図であれ、多かれ少なかれ深刻なプロジェクトは常に特性を持ち、その後に混乱が始まり、プロジェクトは理解できなくなり、検証とテストが難しくなり、制御不能になります。

この境界は開発者ごとに異なります。1つは1000コンポーネントのデバイスを完全に理解でき、もう1つは200コンポーネントのプロジェクトで間違いを起こし、困難を経験し始めます。 一般的に、電子部品の数の見積もりは少し主観的ですが、問題の一般的な本質を理解するのに役立ちます。

上記から、次の結論を導き出すことができます。

開発者がプロジェクトソースの読みやすさと理解可能性を維持するためのアクションを実行する必要がある場合、プロジェクトは複雑になります。

特定の瞬間までは、たとえば次のように、あらゆるものを確実に採点し、ダイアグラムにあらゆる方法で「描画」できます。

すべてが融合し、回路がずさんで、最終的にこれは曲がったり間違ったりする経路につながります。彼らはこの混乱ですぐに気付かず、結果としてボード上の導体を切断し、鼻をはんだ付けしました。

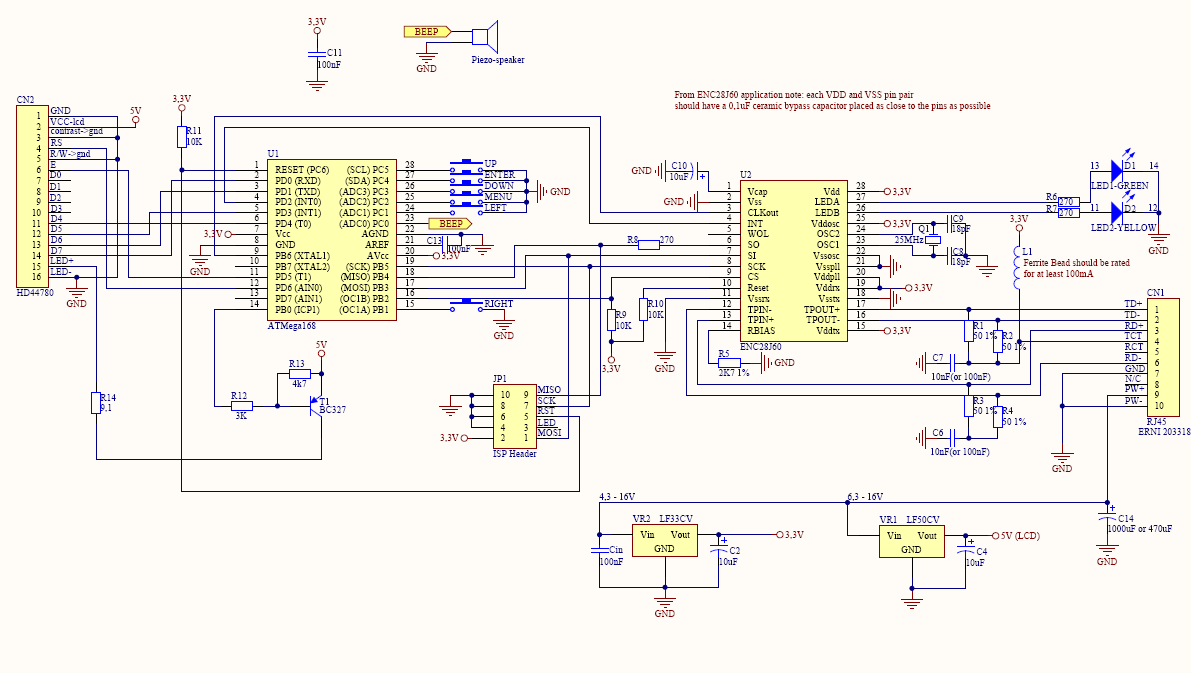

もう1つの傑作を見てみましょう-ADで作られたarduino回路:

どうですか? それは私を傷つけます...私はR2とR3を見て、これらがI2Cのサスペンダーであることは明らかのようですが、このI2Cはどこにあり、どのコネクタが私にとって謎であり、長く退屈なものを探す必要があり、これは少数のコンポーネントを持つ回路ですシンプルですが、すでに混乱しています。

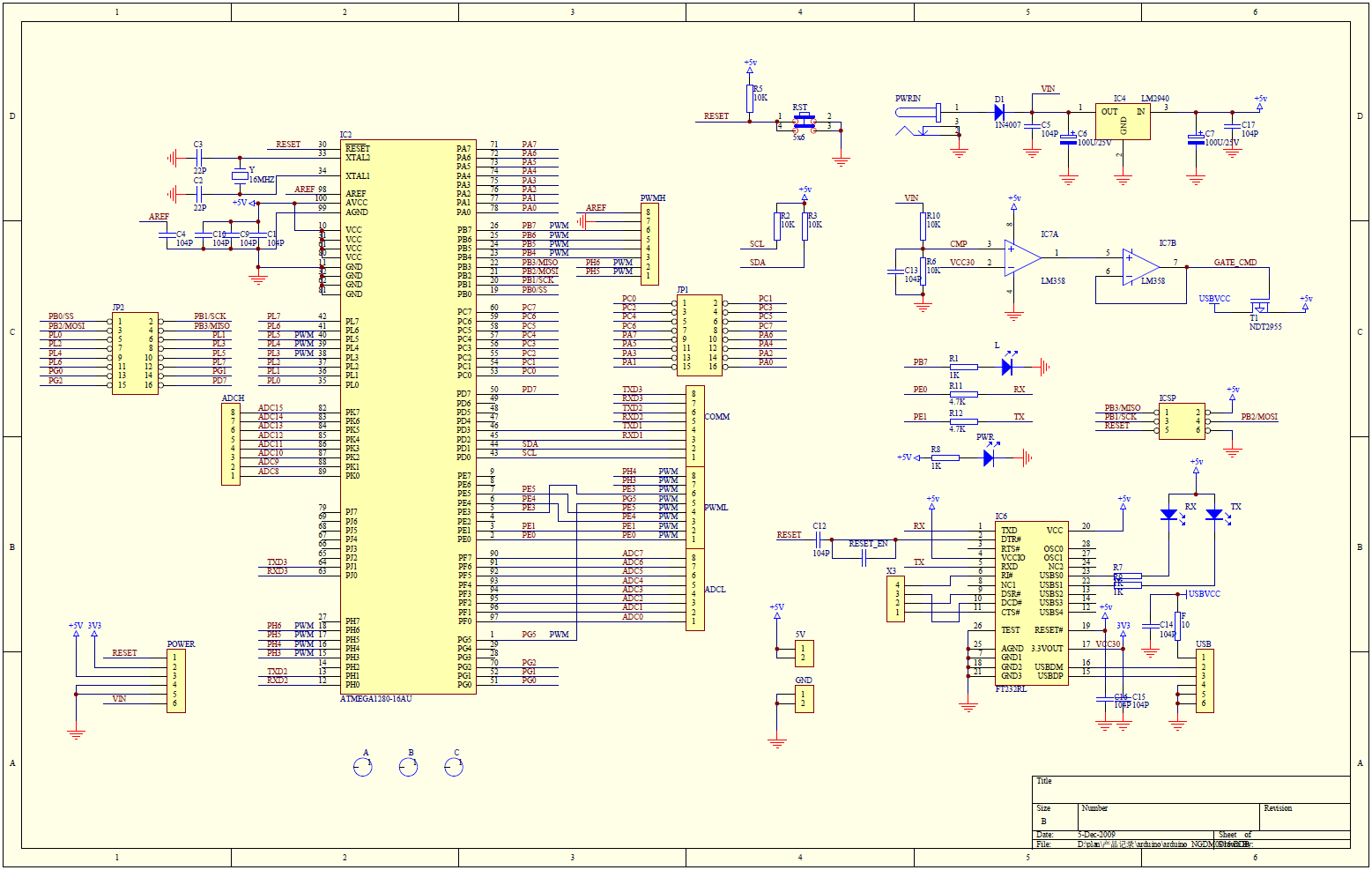

今、代わりとして、私の作品からの例(クリック可能):

スキームを見てください。少なくとも入口がどこにあり、出口がこれを示す「矢印」のヒントであり、アラブ人ではないので、左から右に読んでください。 このモジュールには1つの機能があります-三相コモンモードフィルターのみです。 スキームは慎重に行われ、ドキュメントの1シートを占めます。 1枚-1機能。

実際、私が上で書いたのは、重要で生活を楽にする些細なことですが、それでも些細なことです。 一般的なイデオロギーが得られることを願っていますが、次にその方法を要約しましょう。

- カプセル化の原理は回路にも適用できます。 各モジュールは単一の簡単なタスクを実行します 。 モジュールは通常、ドキュメント内の単一のシートです。たとえば、A3。

- 回路図は、同じスタイルで非常に慎重に実行する必要があります。 将来働くときの正確さは完全に報われるでしょう。 面接でわかりやすく、慎重に実行されたスキームを示すと、すぐに良い印象を受けます。 Rukozhopovはすぐに見られ、通常は好きではありません。

- 数千のコンポーネントがある場合でも、A2より大きいシートを使用しないでください。 A1を使いたければ、何か間違ったことをしていることになります。 おそらく、ダイアグラム上のいくつかのモジュールを選択し、それらを別のシートに転送する必要があります。

批判していますか? 提案する!

今、他の人を批判したので、代わりの「それを行う方法」を提案する必要があります。 記事に記載されている著者の主観的な意見は、実務経験と彼自身の世界観に基づいていることを理解しておく必要があります。

私はすべての普通の人々と同じようにすることを提案します。つまり、まず

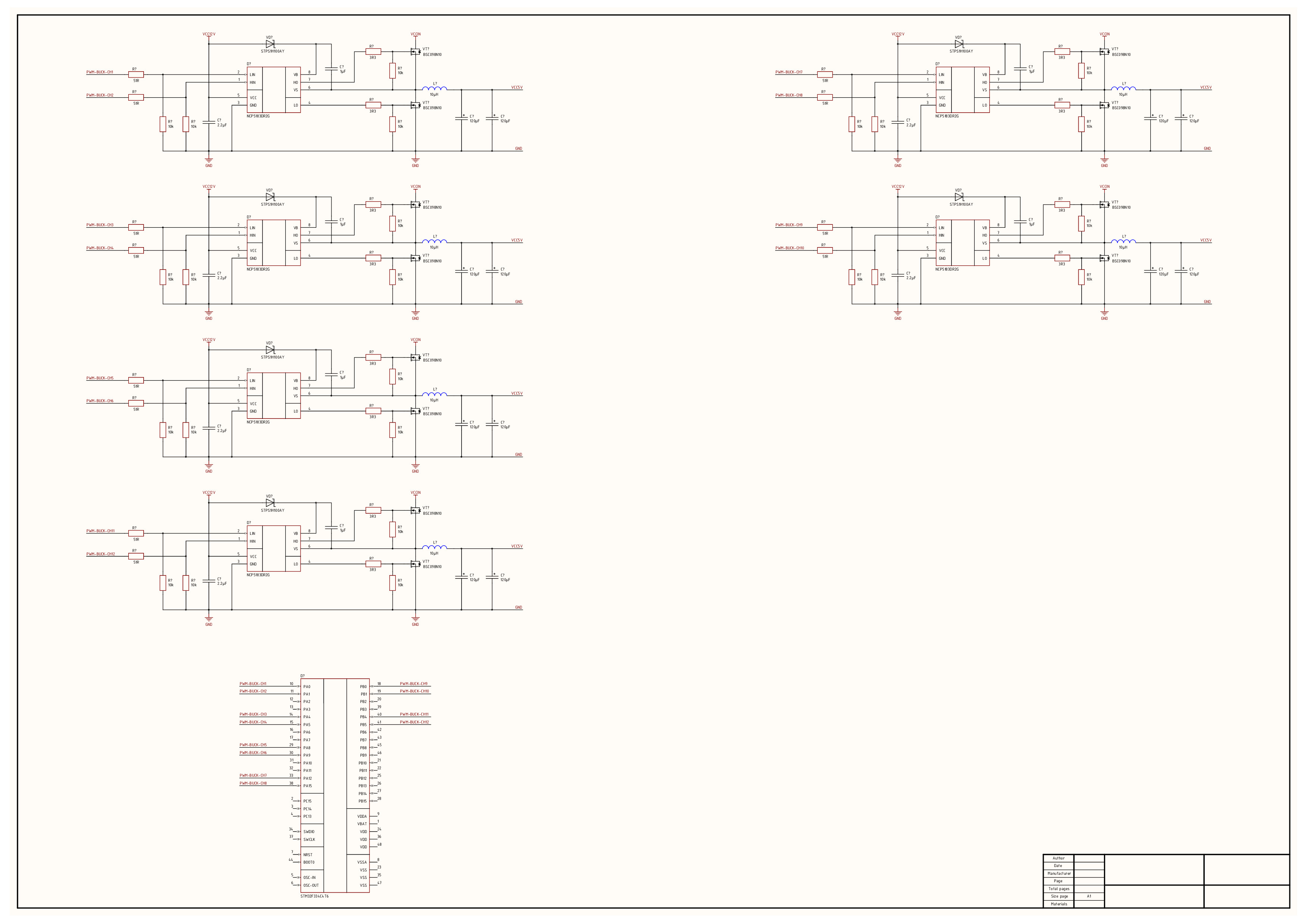

Altium Designerでプロジェクトを作成します。 たとえば、6相の降圧DC / DCコンバーターについて説明します。 すべてのフェーズを制御するために、6つのパワーチャネルと1つのMKがあります。 各電力チャネルは次のようになります(クリック可能):

私がもともと正しく描いたパワーチャンネル自体。 よく見ると、回路に信号入力があります-左側に2 PWM + GNDのVCCIN、出力があります-VCC5VとGND。 モジュール自体が1つのタスクを実行します-VCCINを5Vに変換します。 その後、私たちは不十分...

ここで最初の制限に遭遇します-1つのチャネルがA3のシート全体をほぼ占有し、6つあります。したがって、シートをA2に増やすと、まだ適合しません。 シートをA1に拡大できます-素晴らしい、今のところ私たち

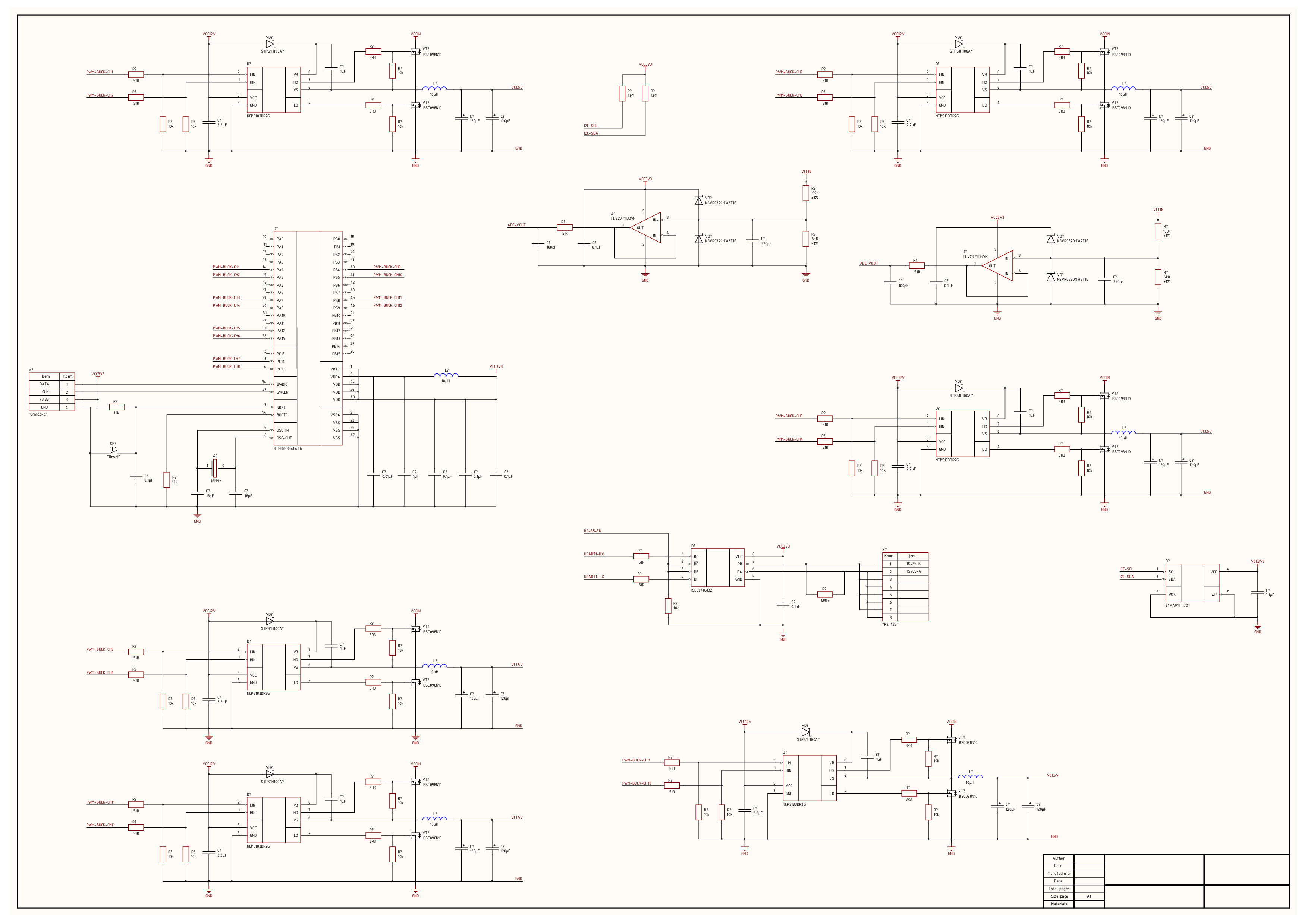

今のところ明らかなようです-回路は6個あり、下にMKがあります。 それはスキームのわずか30%です。他に何が必要ですか? MKバインディング+フィードバック? もちろん! デバイスは外部と通信する必要がありますか? もちろん、RS485を追加します。 ああ、ドライバーにはまだ電源が必要です。つまり、VCCINから+ 12Vを取得し、このためにDC / DCを追加する必要があります。 別のMK ...彼はもう1つのDC / DCを必要とし、これをすべて追加します-見てください(クリック可能):

何があるのかは明らかですか? デバイスの機能について最初に言わなかった場合はどうなりますか? そして、これに加えて、彼はまた回路の不器用な部分を不器用に描いたとしたら? また、ライブラリ内のUGOコンポーネントが最初に曲がって描かれている場合はどうなりますか? 怖い? それは同じです...

どうする?

今考えてみましょう...このデバイスには、全部で150個のコンポーネントがあり、パワーエレクトロニクスに関連する私の平均的なプロジェクトでは、それらは通常1500から4000です。つまり、上記のようなA1のシートが10枚あり、それらがすべて散らばって詰まっているときの災害の規模です。 間違いは避けられません!

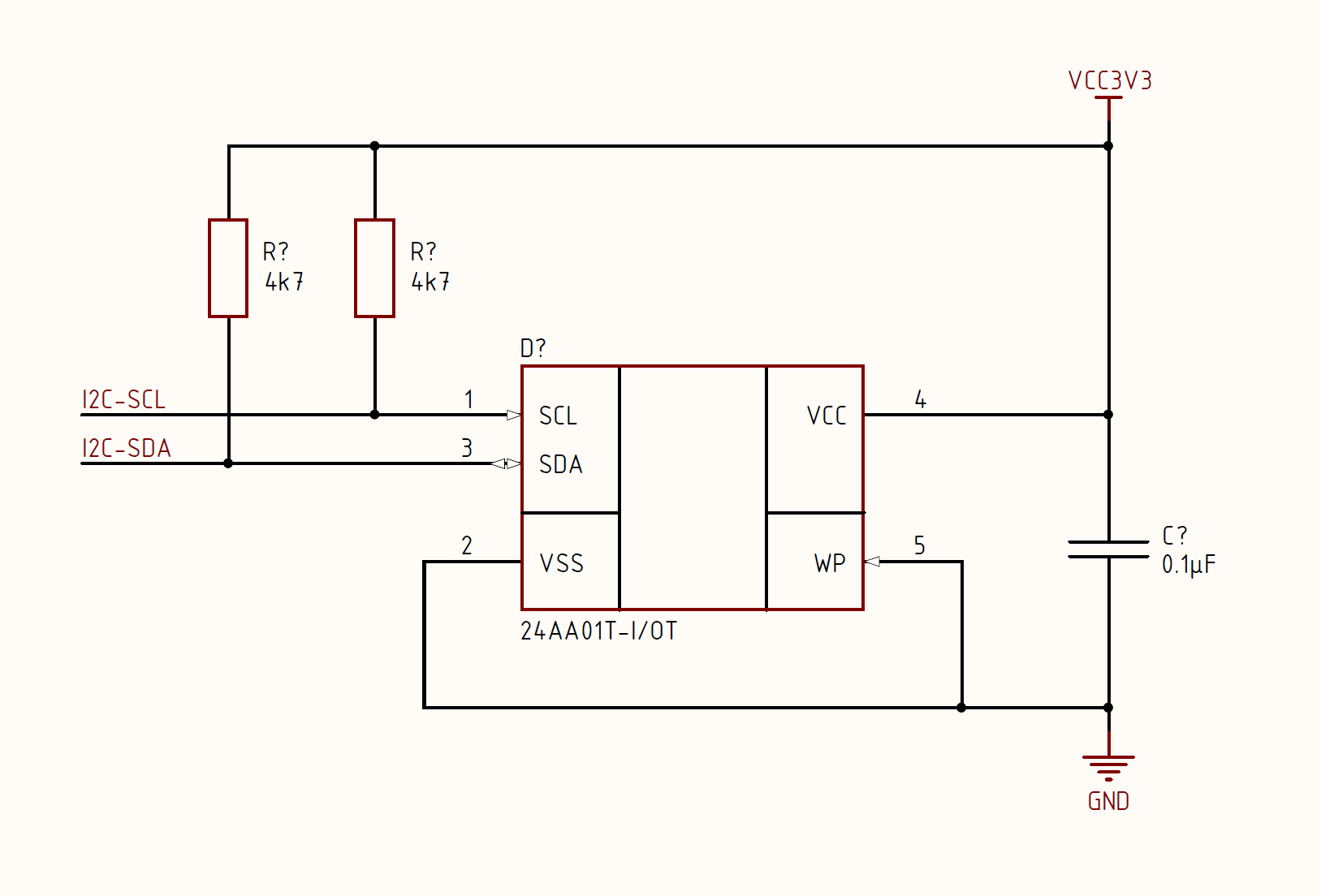

さらに調べて考えます。 最初に行うことは、モジュールを形成することです。 私はそれらをすべて形成しました、なぜなら 1つのホームクラフトからコピーしただけですが、1つのモジュール(I2Cで実行されているEEPROMメモリ)を破損しました。 私はArduinoスキームと同じ間違いをしました、それを行う方法:

ご覧のように、メモリチップを1つの「ヒープ」にまとめて、電力コンデンサをブロックします。電力コンデンサは、近くにあり、+ 3.3Vにプルアップします。 メモリチップを結ぶために必要なすべてのコンポーネントの図を見る必要はありません。それらはすべて1か所にあります。 ちなみに、小さなチップごとに個別のシートを割り当てる必要はありませんが、EEPROMは個別のモジュールではなく、マイクロコントローラのバインディングの一部です。 ストラップ付きMK-これは、別のシートにふさわしいモジュールです。

先に進みましょう...回路の繰り返し部分があります。たとえば、オペアンプ(OA)のフィードバック用に2つのまったく同一のチャネル、6つのより完全に同一のパワーチャネルがあります。 これも最適化できます。

別の明るい考えは、6つの降圧チャネルがすべて同じである場合、そのトレースはほとんど同じであるということです。 これを使用する必要があります。 たぶん、あなたは1つのモジュールのために道路を作ることができます、そして、残りの5は「よく、繰り返します」と言いますか? ADにより、私たちの生活が大幅に簡素化されることがわかりました。

美しくやろう!

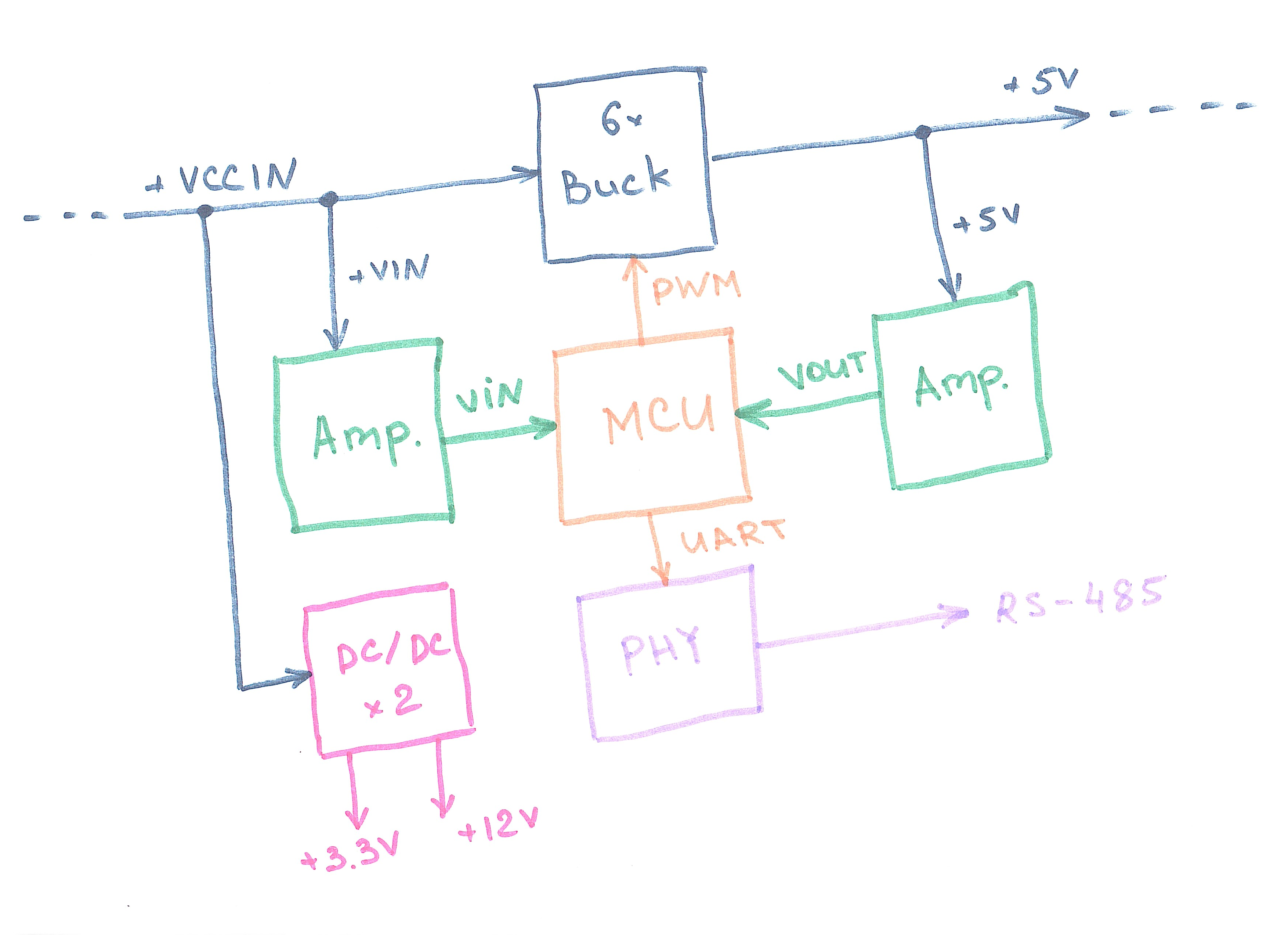

電子機器はどこから始まりますか? もちろんの考えで。 このアイデアを具体的なものに変えるには? たとえば、マクロ機能が表示されるブロック図を描くことができます。 非常にスマートである必要はなく、黒板や紙に絵を描くだけです。

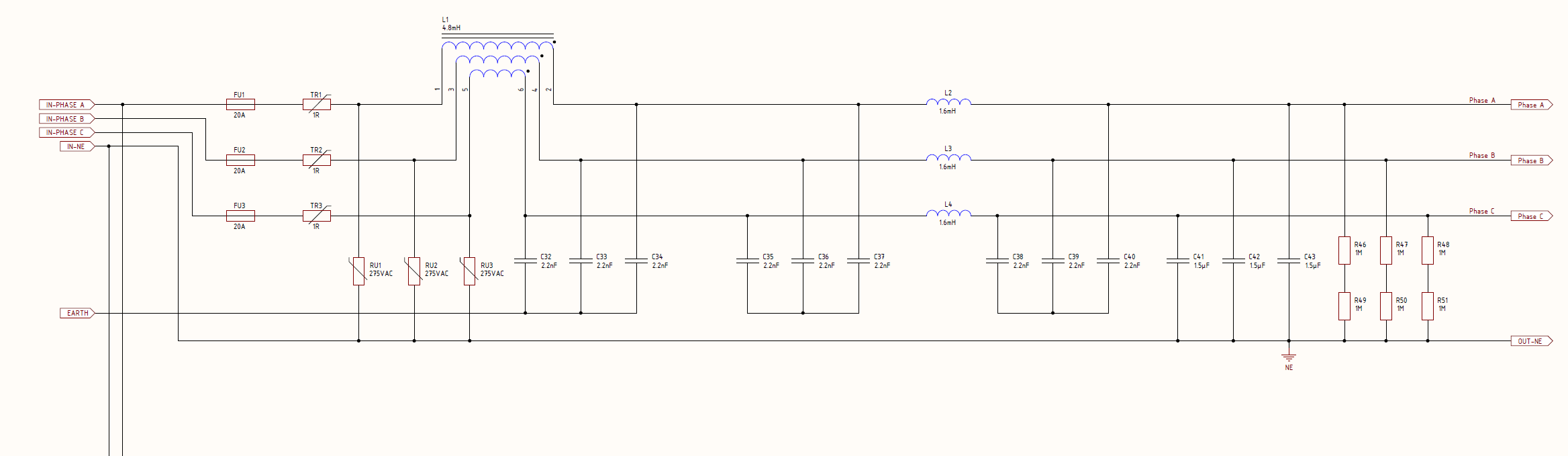

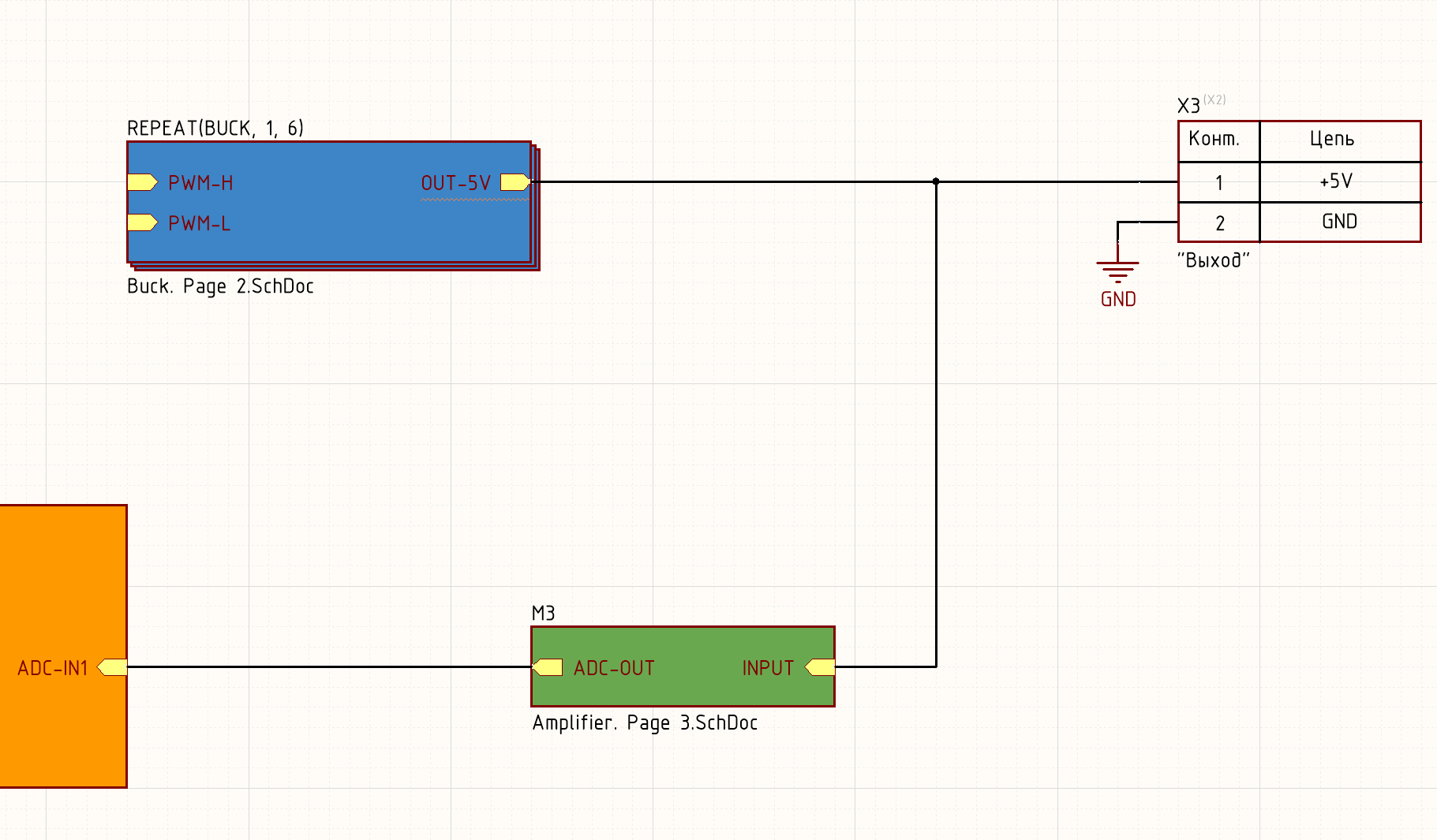

シートには、デバイスのすべての機能が収まります。 まず、この回路により、デバイスの基本的な動作を理解できます。MCUによって制御される6チャンネルの電源部(バック)があり、制御のためにオペアンプ(アンプ)を介して2つのフィードバック信号が生成されます。セルフパワー用のDC / DCと世界との通信用のModbusインターフェイスがいくつかあります。 第二に、スキームによると、既製の機能ブロックがすぐに表示されます。

次に、ADで5枚の3を作成し、回路の対応する部分をそれぞれに転送する必要がありますが、その前に、ADで使用する接続と回路の種類を考慮する必要があります。

- 電源ポート

このタイプは、プロジェクト全体でグローバルです。 つまり、このようなポートをあるシートと別のシートに配置すると、「VCC3V3」という名前の単一の回路にマージされます。 したがって、さらに、異なるシート上の電源回路を接続する必要はありません。 このタイプのポートは、電源とグランド(GND)のみを定義します。 - ネットラベル

回路内の特定の回路に名前を付けるためのツール。 同じ名前のチェーン(NetLabel)は、単一のシート内とそれ以外の両方で結合されます。 このツールは、1つのシート内で名前と接続を指定するためだけに使用します。 - ポートを配置

モジュール間接続のためのツール。 モジュール/シート内の接続に使用されるNetLabelとは対照的に、このポートは「外の世界」との通信に使用されます。 モジュールを互いに接続します。電源とグランド(GND)を除くすべての回路。

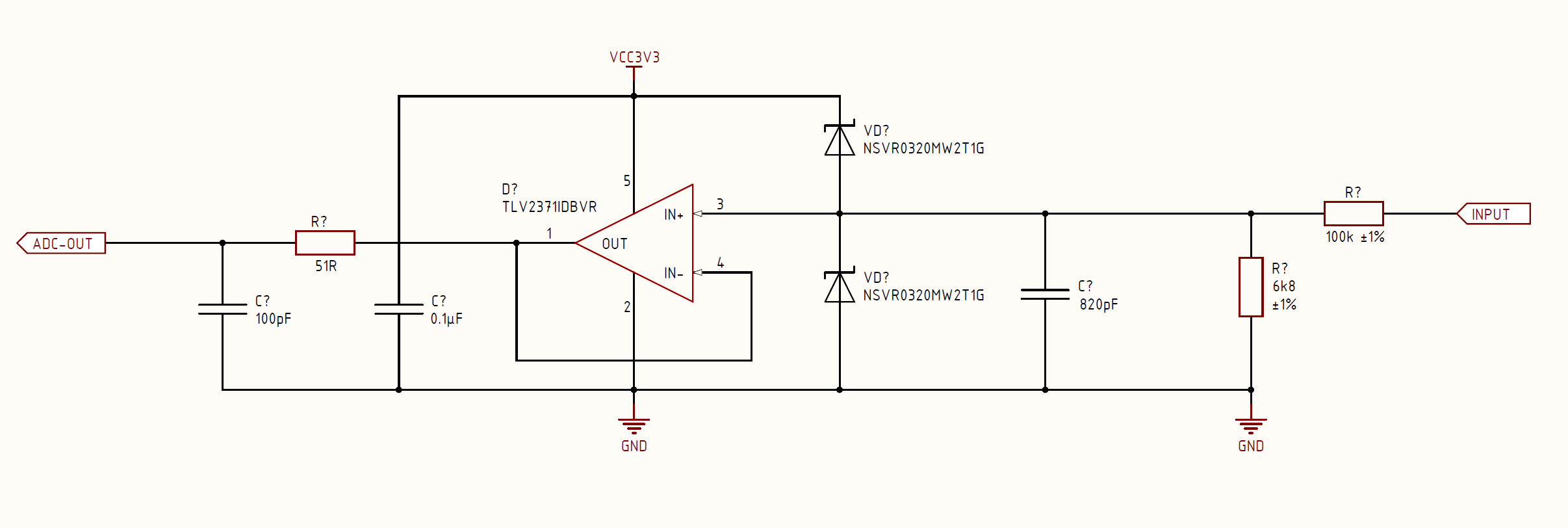

ここで、Place Portを使用して、モジュールを超える信号を設定する必要があります。 たとえば、オペアンプを備えたモジュールの場合、次のようになります。

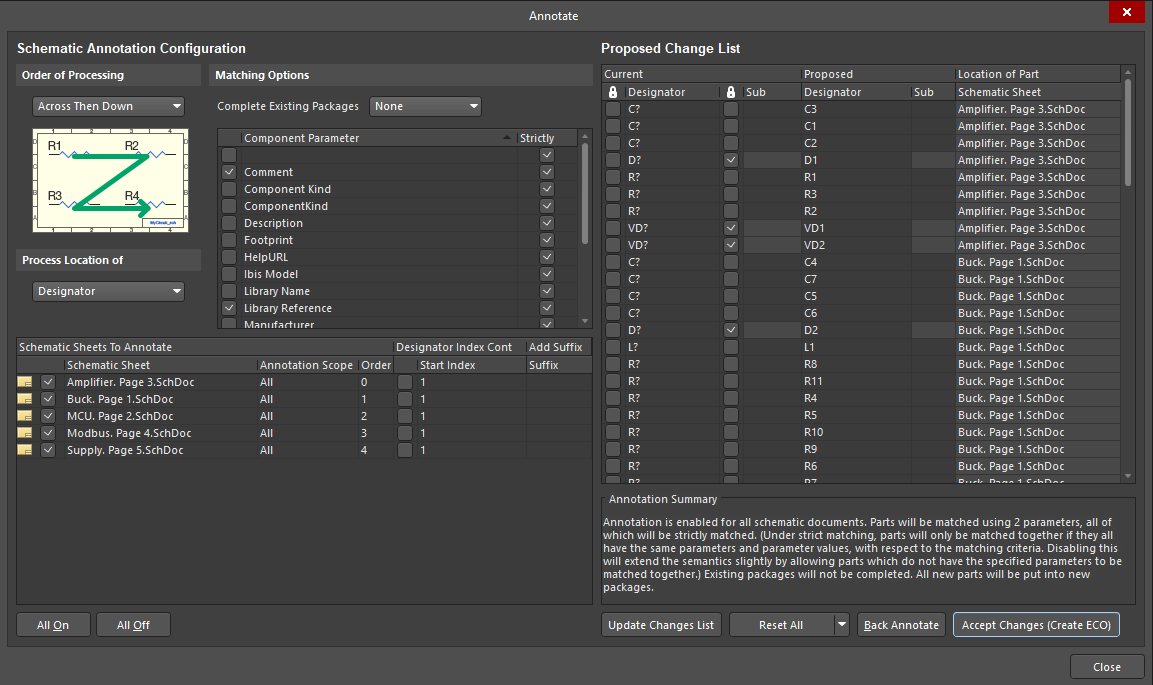

これで、モジュールは回路の完全に論理的な部分になりました。入力(INPUT)、出力(ADC-OUT)、および2つのグローバル接続(電源ポート)-GNDおよびVCC3V3を備えています。 これ以上。 他のモジュールについても同じことを行い、 [ツール]-> [注釈]-> [回路図に注釈を付ける]をクリックし、[ 変更リストの更新 ]をクリックして、記号(指定子)に番号を自動的に割り当てます 。

次に、[ 変更を承認 ]をクリックし、開いたウィンドウで[ 変更を実行 ]をクリックします。

余分なウィンドウを閉じて、指定(D?、R?、C?など)が一意の番号を受け取ったことを確認します。 アクションが完了すると、ここでそのようなプロジェクト-PDFを取得します。

まあどう? 私は誰も議論しないと思う-すべてがきちんとしている、それが一見してどのように機能するかは明らかであり、図にはゴミがありません。 今は小さなものにとどまります-1枚のシートから6チャンネルを作成し、通常はすべてを1つのヒープに結合する必要があります。

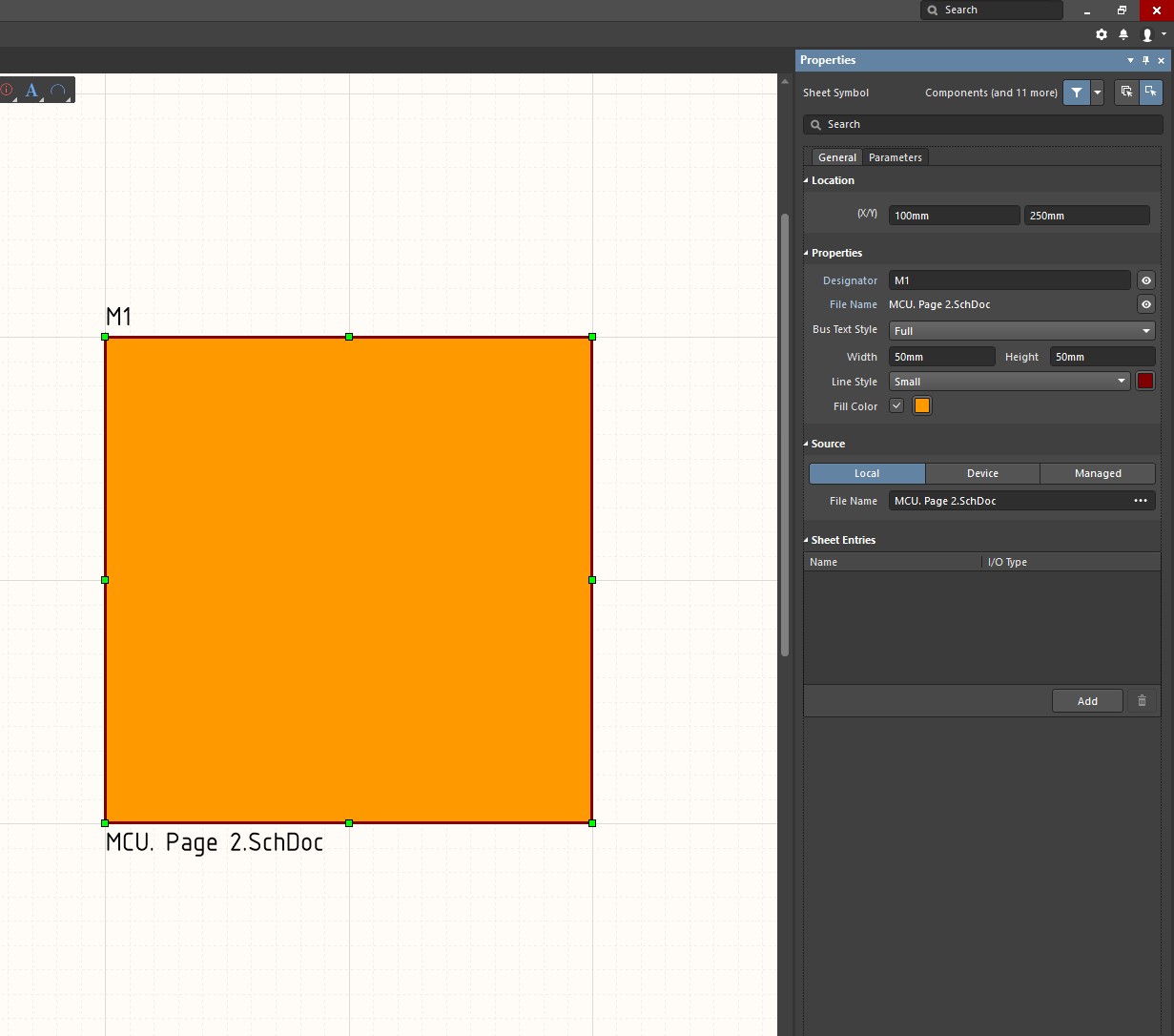

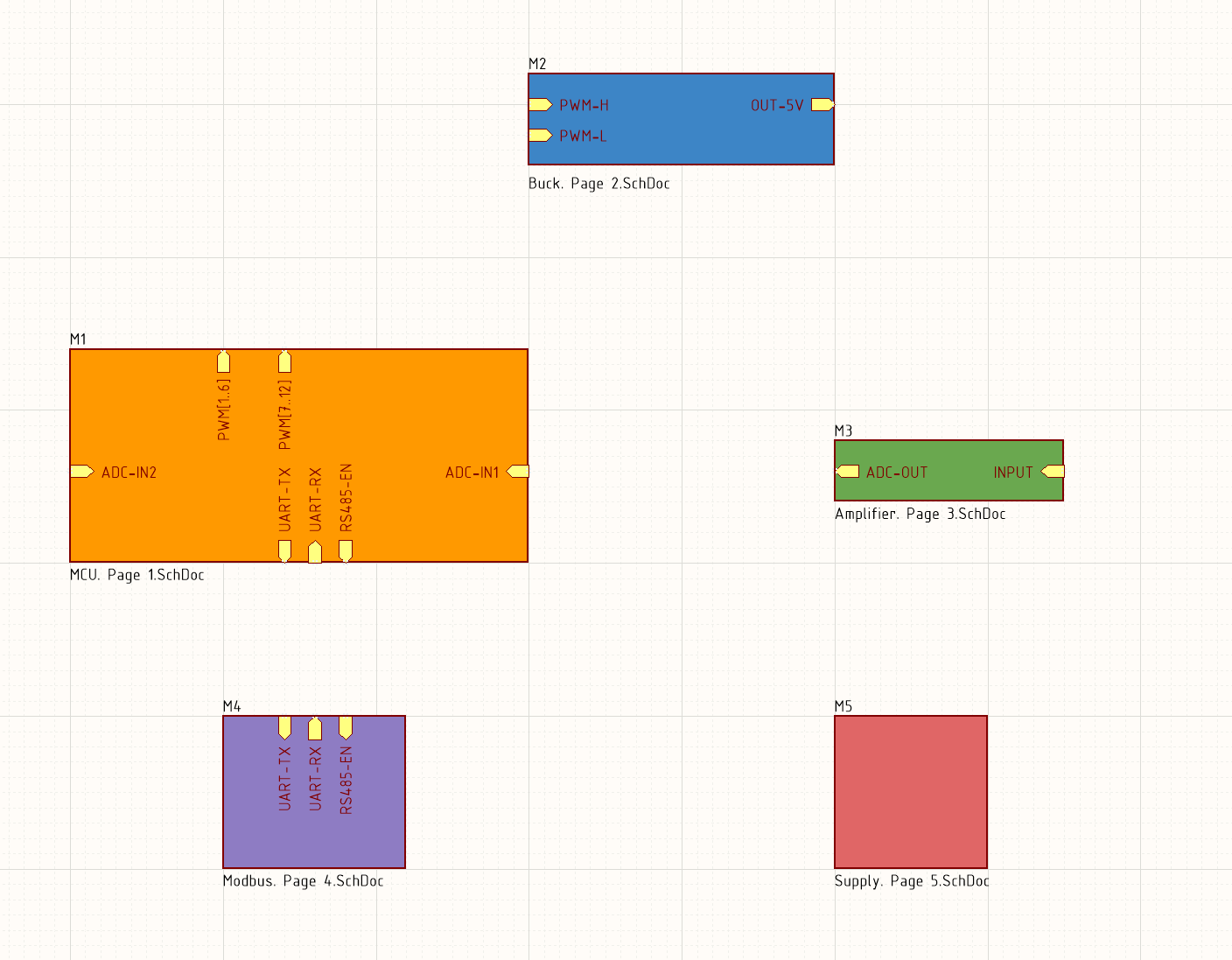

これを行うには、新しいシートを作成し、 Main designという名前にしますが、名前は何でもかまいません。 このシートには、以前に手で描いたブロック図があります。 モジュールを作成するには、 [配置]-> [シートシンボル]に移動します。 次に、要素全体にプロジェクト全体のスタイル、つまりフォント(ISOCPEURがあります)、フレームの幅と色、指定子などを指定し、モジュールにシートの名前を記述します。

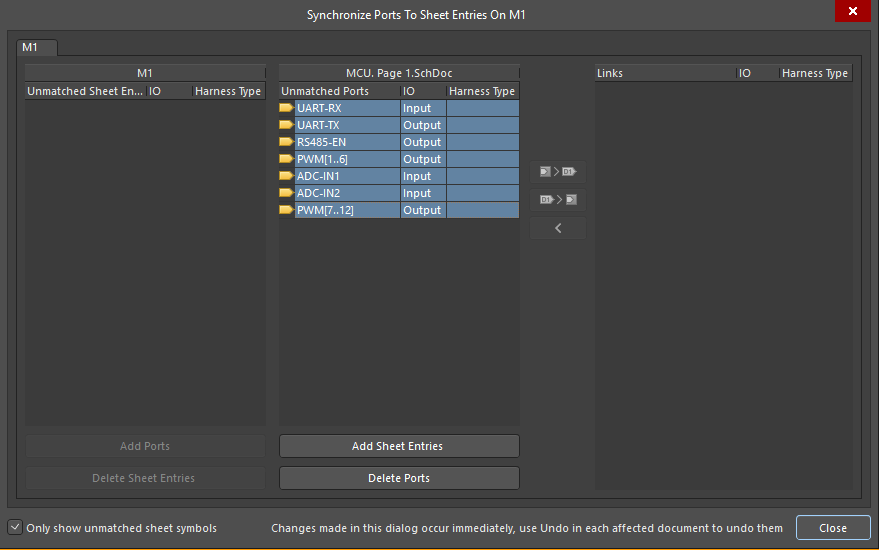

モジュール(オレンジ色の正方形)を右クリックして、 シートシンボルアクション->シートエントリとポートの同期を選択すると、ウィンドウが開きます。

その中に、Place Portのリストがあります。 すべてを選択して[ シートエントリの追加 ] をクリックし、モジュールにインストールして、フォントの一般的な種類を設定すると、次のモジュールが取得されます。

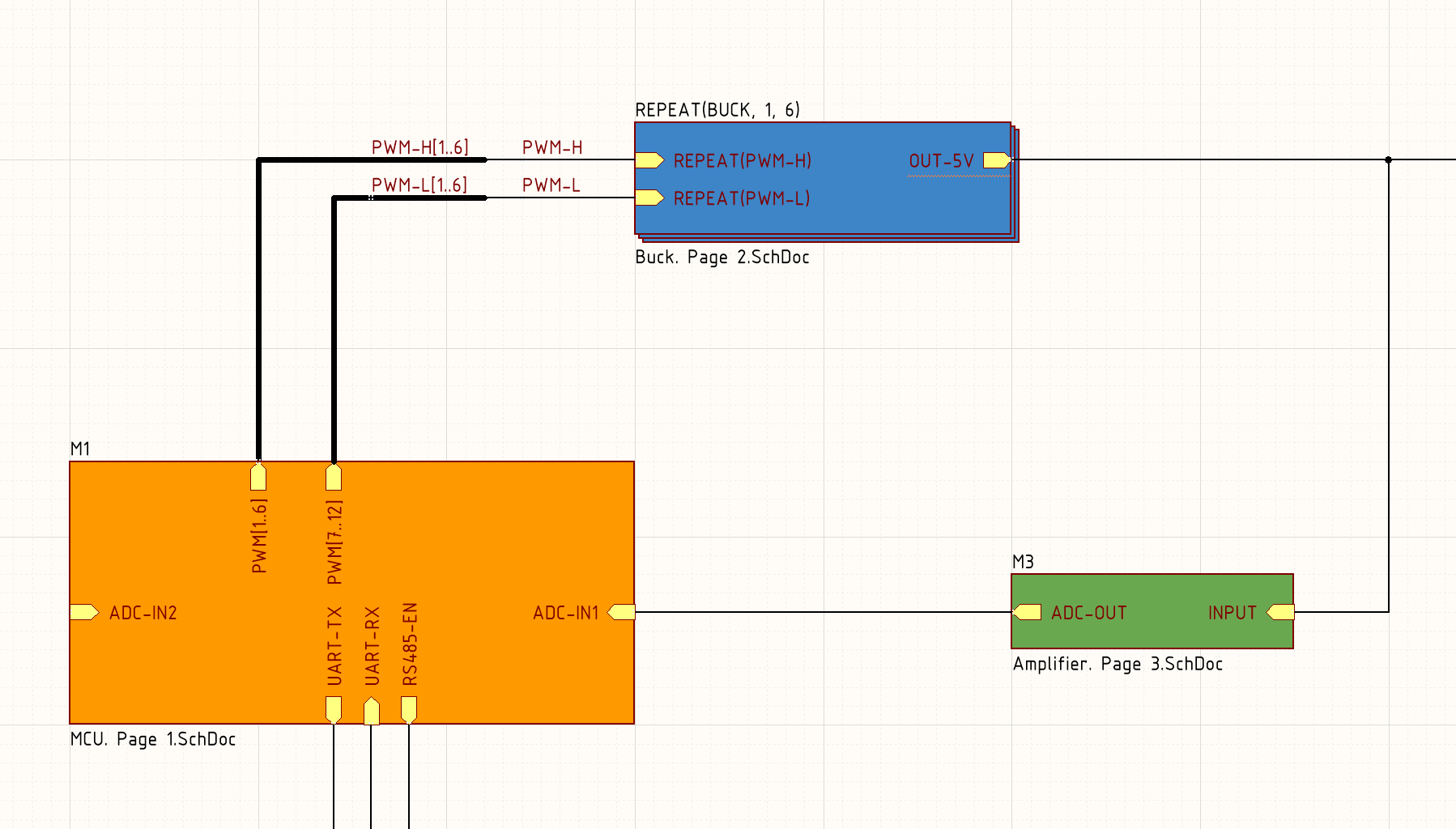

残りの4つのモジュールについて同じことを繰り返し、出力でこの構造を取得します。

ここでは、2つの点に注意する価値があります。

- dc / dcの5番目のシート(ページ5)は、同期しようとするとPlace Portを検出せず、モジュール図を見ると、実際には存在せず、Power Portのみです。 しかし! 確実にモジュールを取り出す必要があります。そうしないと、このシートのコンポーネントがボードに表示されません。

- [ポートの配置]ツールには、入力、出力、および双方向の指向性パラメーターがあることに注意してください。 信号のポートのタイプを正しく決定する必要があります。たとえば、PWM-HポートはMCUの出力で、降圧の入力です。

クローン

すべてのモジュールを作成したので、パワーセクション用に6チャネル、オペアンプ用に2チャネルを得るために、モジュールの数を増やす必要があります。 ことわざにあるように、たとえあなたが食べられたとしても、常に2つの出口があり、この場合も例外ではありません。 両方の方法を示します。

- 直接コピー

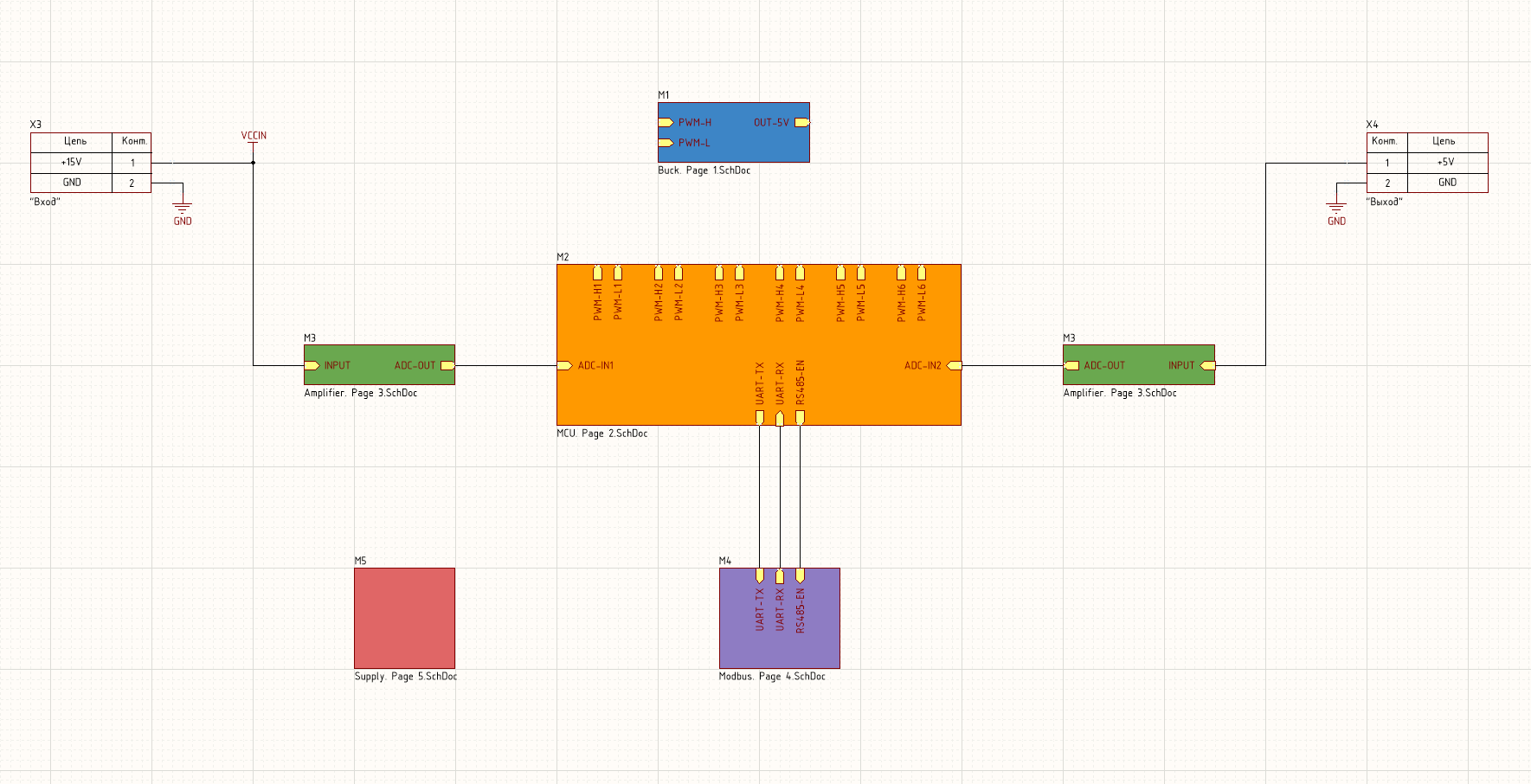

ここではすべてが簡単です-通常のコピーアンドペースト。 モジュールを選択し、Ctrl + CおよびCtrl + V-新しいモジュールを取得します。 指定子番号をM3からM6に変更するだけです。 次に、すべてを接続して、回路の中間バージョンを取得します。

オペアンプモジュールをコピーし、いくつかのコネクタとGNDおよびVCCINバスを追加しました。これらはグローバルになり、見つかったすべてのモジュールですぐに接続されます。 この場合、それらを別々にドラッグしてポートを配置することは意味がありません。 また、Buckモジュールを除くすべての外部回路を接続しました。その上で、2番目のよりコンパクトな方法を示します。 - ジェダイのコピー

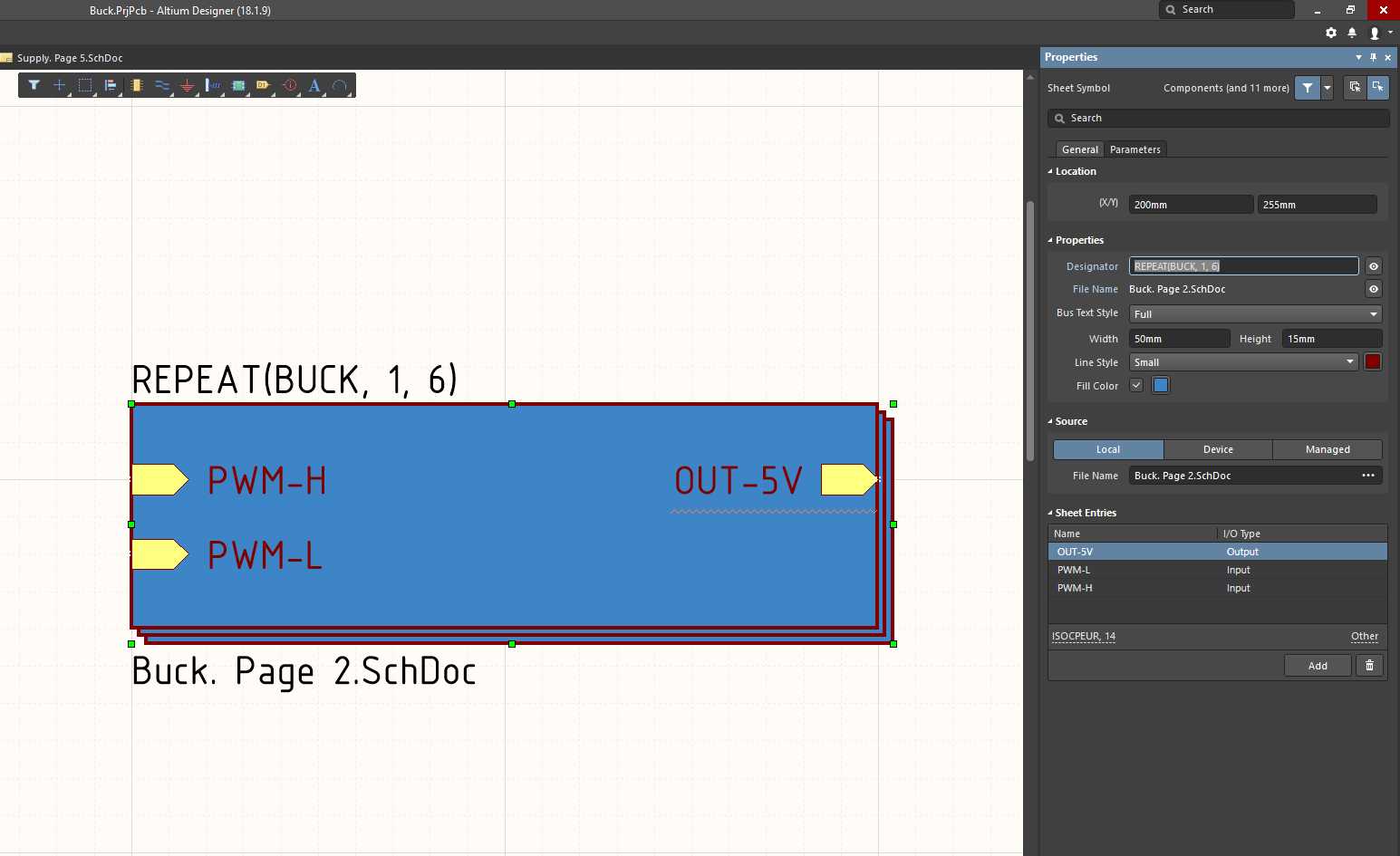

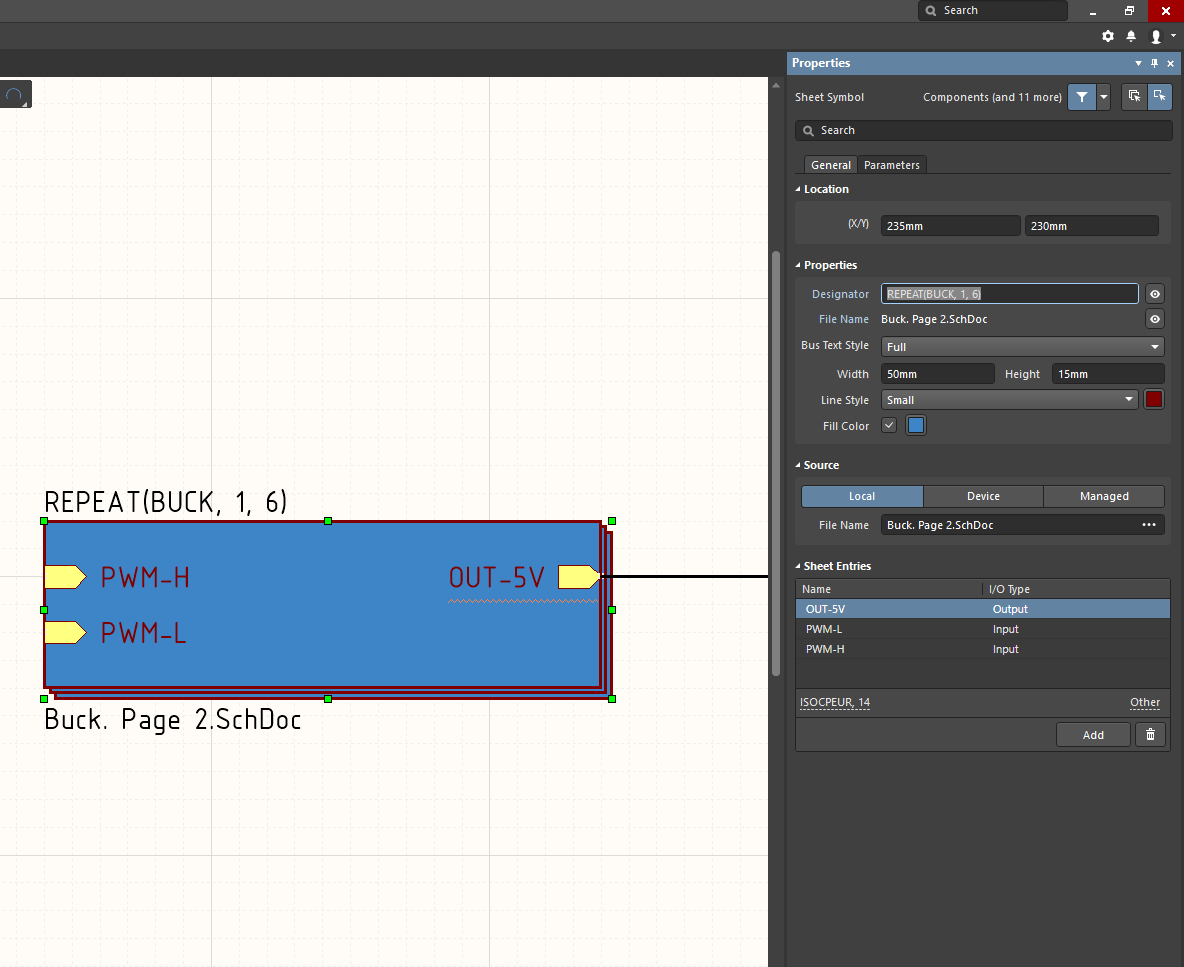

前のバージョンとは対照的に、ここではすべてを理解することは困難ですが、実装はより簡単で、最も重要なことはより有能です。 REPEATディレクティブを使用して、複数のチャネルが作成されます。 このために、指定子M1の代わりに、 REPEATコマンド(BUCK、1、6)を作成します。 このチームは、BUCK1からBUCK6のデジグネーター、つまり6個のチャンネルを作成します。 Enterキーを押して、ADが必要な数のチャネルを作成した方法を確認します。

次に、回路を接続する必要があります。 シンプルなものから始めます-すべてのチャンネルのOUT-5V出力を組み合わせる必要があります。 すべてのフェーズは、共通出力用の1つのコンバーターとして機能します。 これを行うには、Place Portから通常の回路を描画し、出力コネクタに接続します。

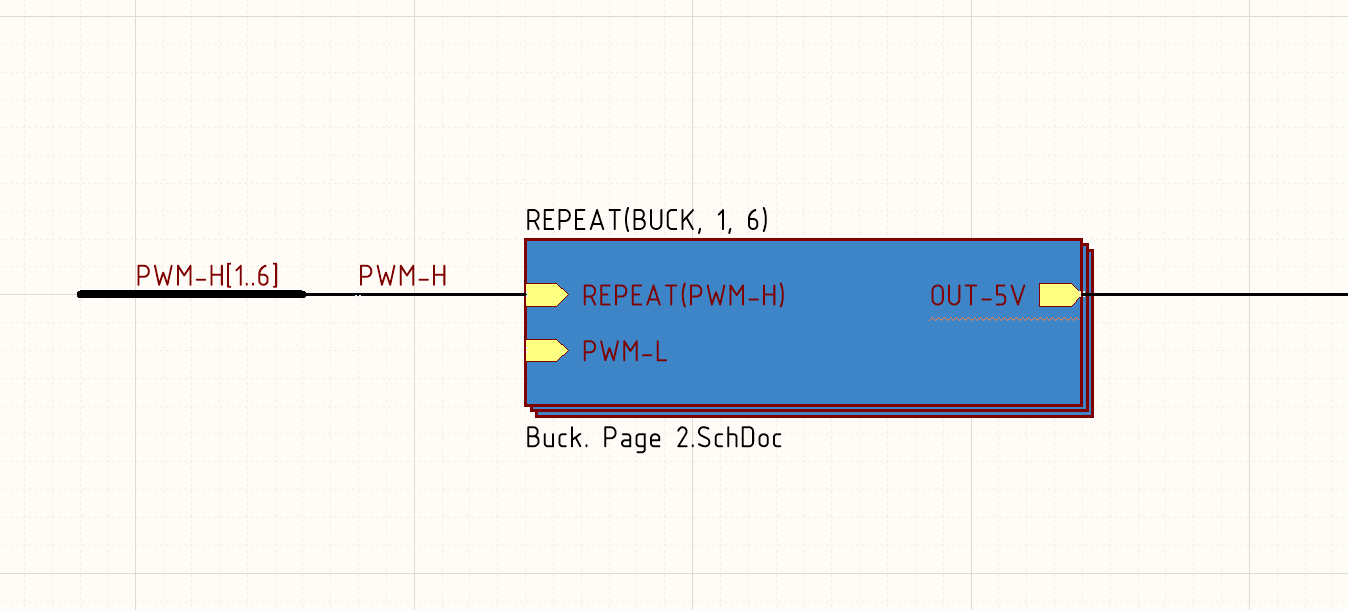

ここで、ADにPWM-Hポートが1つのポート/回路ではなく、6つの個別のチャネルであることを伝える必要があります。 これを行うには、PWM-Hという名前のポートの配置をクリックし、名前の列にREPEAT(PWM-H)と記述します。これにより、6つの異なるチェーンが作成されます。

次に、REPEAT(PWM-H)という名前の配置ポートから通常のチェーン(Ctrl + W)を出力し、NetLabelツールを使用してこのチェーンにPWM-Hという名前を付ける必要があります。 次に、回路からバスを削除し、 PWM-H [1..6]という名前を付ける必要があります。 したがって、1つのポートから、PWM-H1、PWM-H2などの名前を持つ6つの異なる回路を導出しました。

次に、 PWM-Hバス[1..6]を上部ハーフブリッジトランジスタのMCUモジュールのバス出力に接続します。 同様の手順は、下側のトランジスタに対しても実行する必要があり、バスをスローする必要があります。最終的に、次の形式の回路ができます。

Zenがわかったので、コピーペーストの形で松葉杖を残さないように、オペアンプでJediモジュールを作り直しましょう。 その結果、回路図の最終バージョンが得られます。

これで回路図で終わります、最終結果はPDFです。 ご覧のとおり、最も単純なスキームが出てきました。わずか数枚の空のA3シートがあり、時間と神経が最小限のアマチュア無線オペレーターなら誰でも理解できます。

トレースごとに数十時間を節約

現代の現実では、コンポーネント(超小型回路)の集積度が非常に高い場合、回路図の作成にかかる時間はますます短くなります。 まだそれほど頻繁ではないのに、90%のアナログモンスターに出会うでしょう。これは良いことです。 デバイスの開発プロセスにおける「弱点」は、プリント回路基板(PCB)の設計のままです。 最新のCADシステムには、ボード開発の人件費を削減するためのさまざまなツールが用意されており、これがこの記事の主な目標でした。

前に指摘したように、このデバイスには複数の繰り返しモジュールがあります:バックおよびオペアンプ。 最新のデバイスを見ると、たとえば、すべてのチャンネルが同一である4チャンネルのオシロスコープなど、多くのデバイスでこのような繰り返しが発生します。 もちろん、各チャネルを手でトレースすることができ、生活を簡素化できます。

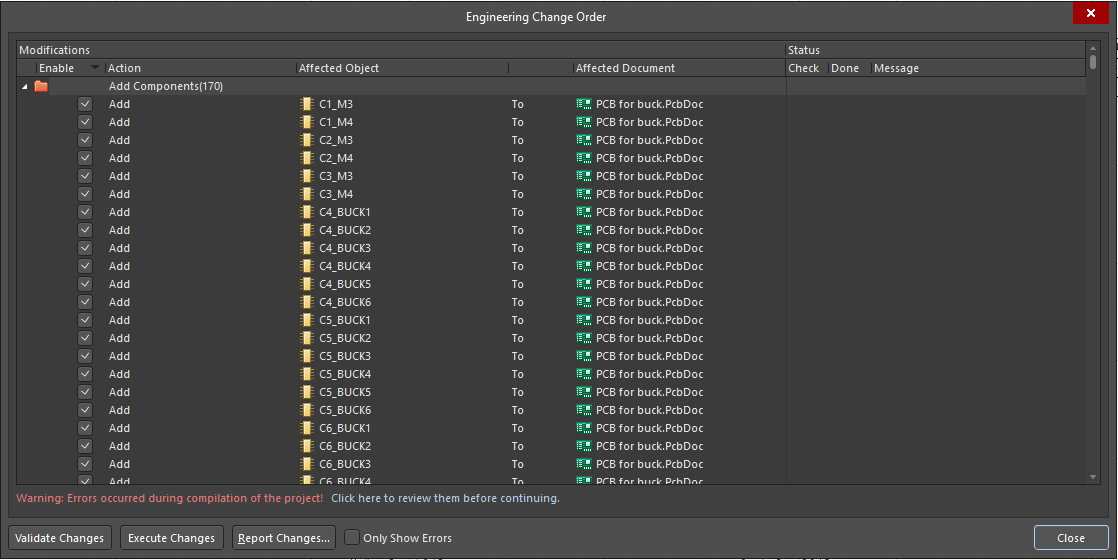

この記事で以前に説明されたすべてのことは、単純に呼ばれます- マルチチャネルスキームは 、シンプルで上品です。 このような回路図を作成しましたが、次のことができるようになりました-1つの降圧チャネルの回路を分離し、残りの5つとコンポーネント(レイアウト)とすべての導体の位置に単純にコピーします。 最初に、すべてのコンポーネントを回路図から回路基板のファイルに転送し、[ デザイン ] -> [PCBドキュメントの更新 ]をクリックします。

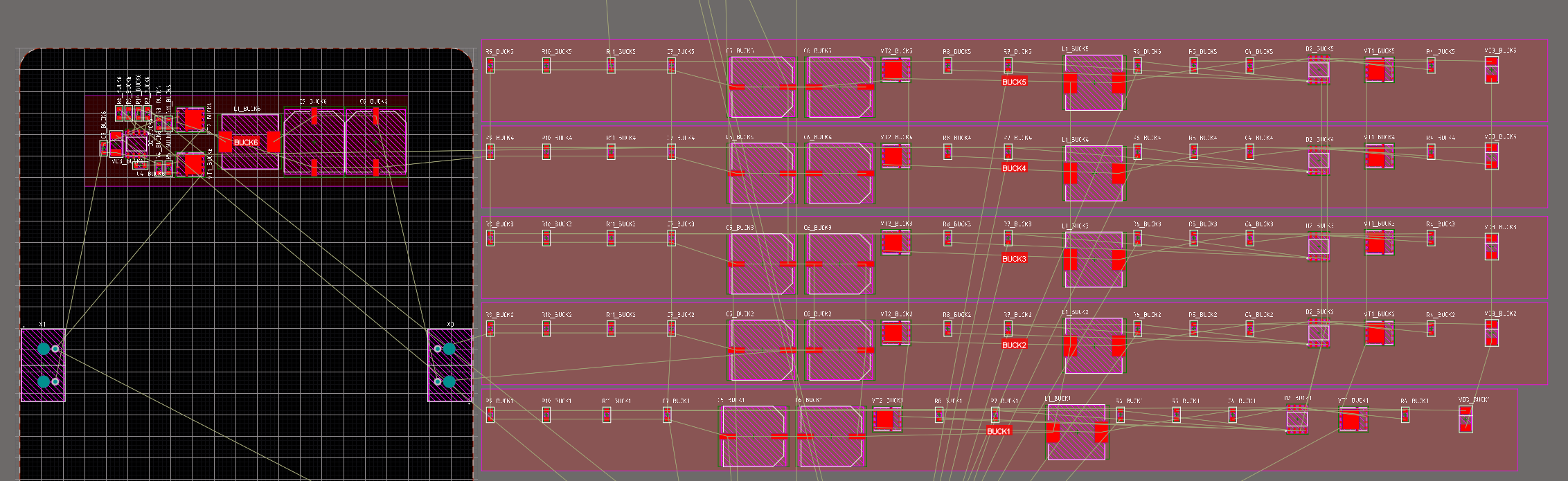

[ 変更の実行 ]をクリックすると、そのようなプリント回路基板が得られます。

ご覧のように、ボードと呼ばれる6つの赤いゾーンが部屋と呼ばれています。 各部屋には、1つのチャンネル用の電子部品があります。 次に、部屋の大きさを設定する必要があります。つまり、チャンネルのコンポーネントが占める特定のエリアを指定し、詳細のレイアウトを作成する必要があります。 次のようになります。

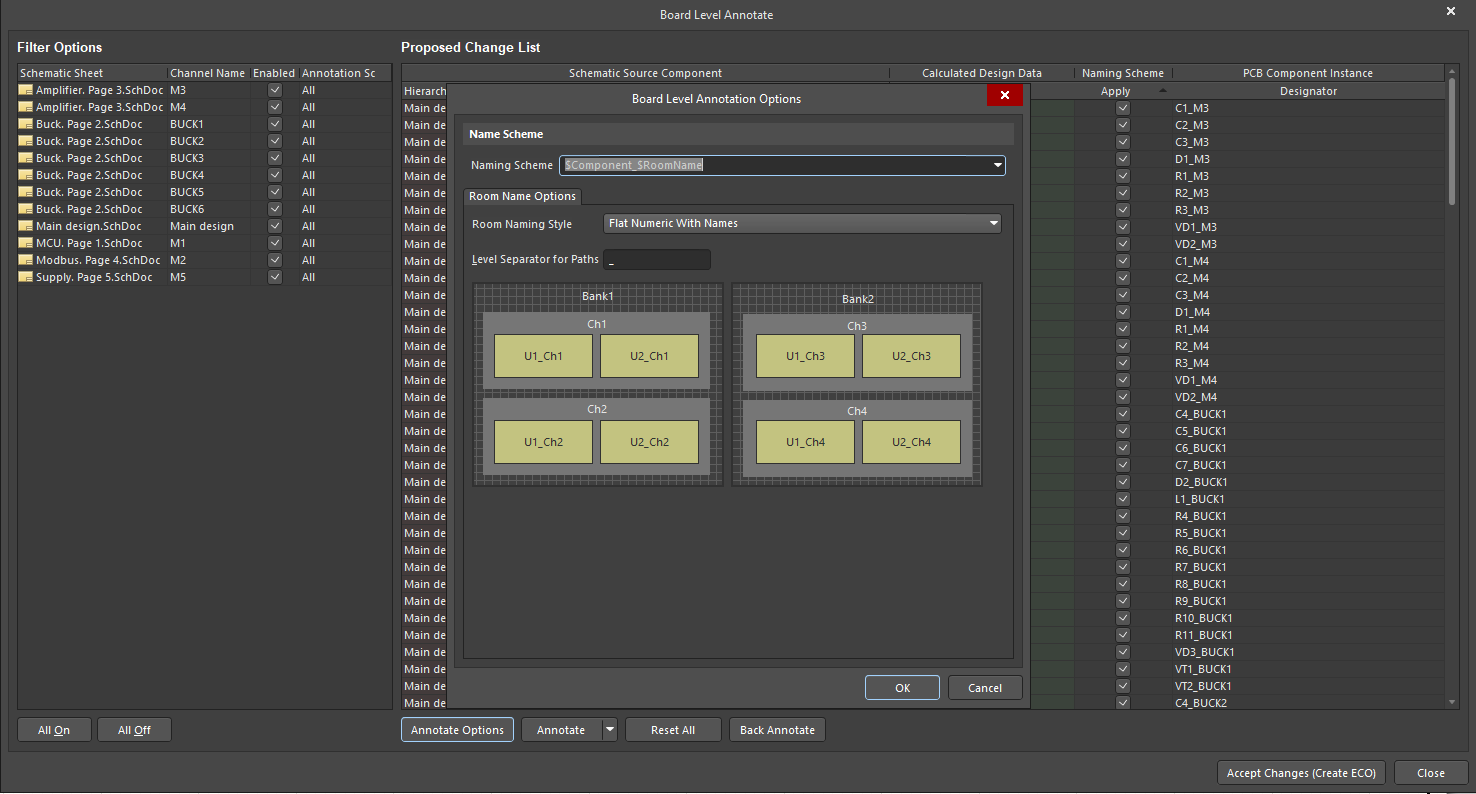

そのため、各チャネルのコンポーネントが配置され、そのような領域を占有します。 確かに、私はここで何かが好きではない...うん! シルクスクリーンレイヤー(白いラベル)のコンポーネントの指定には、エンドツーエンドの番号付けはありませんが、「Room_Name」という形式の番号付け、つまり抵抗器R6_BUCK1、R6_BUCK2などがあります。 接頭辞「_BUCK1」を避けたいのですが、各コンポーネントには独自の番号があります。 Ctrl + Lを押して、 [ 注釈オプション ]メニューに移動すると、次のようなメニューが表示されます。

次に、番号付けオプション$ ComponentPrefix $ GlobalIndexを選択して、[OK]をクリックする必要があります。 [ すべてリセット ]をクリックしてすべての値を破棄し、[ 指定の注釈 ]をクリックします。 BUCK2チャンネルで見ることができるように、コンポーネントはR6_BUCK2からより馴染みのあるR6、R7などに変更されました。

[変更を承認]をクリックして変更を承認し、開いたウィンドウで[ 変更を実行 ]をクリックしてすべてを確認します。 変更を回路から設計-> PCB Documet回路基板の更新に転送します。 その結果、ボード全体を占有しない「人間」の指定を観察し、その中にガタガタします。

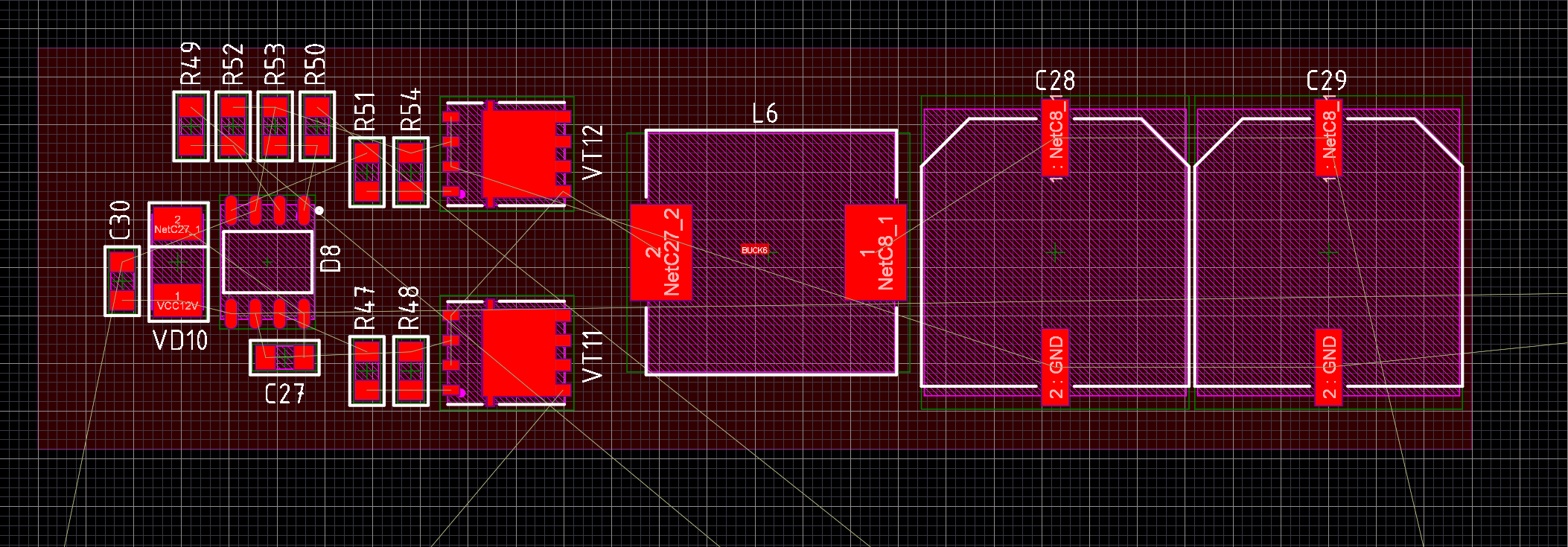

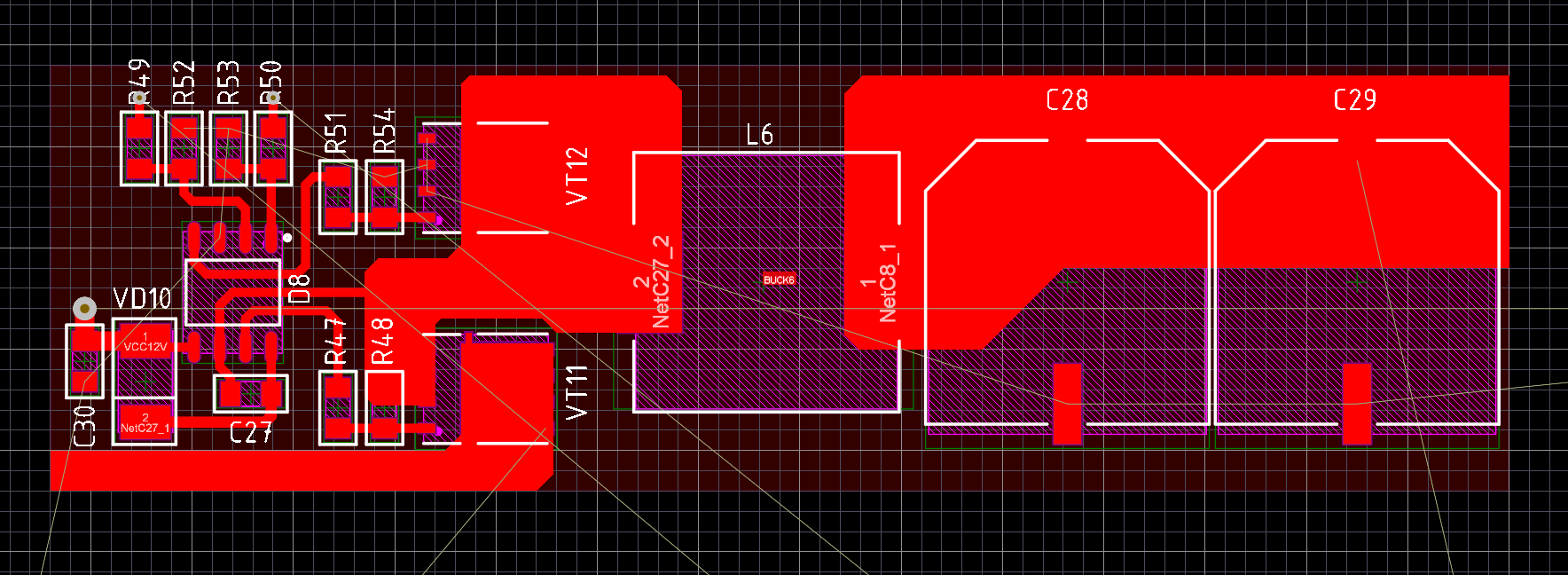

適切なレイアウトと指定ができたら、トレースに進みます。1つのBUCK6ルーム内の回路をトレースして、次の図を取得します。

私はすべてを繁殖させたわけではありません。 通常、これは単一のポリゴンで埋められます。 デモンストレーションには十分です。 次の手順を実行します。

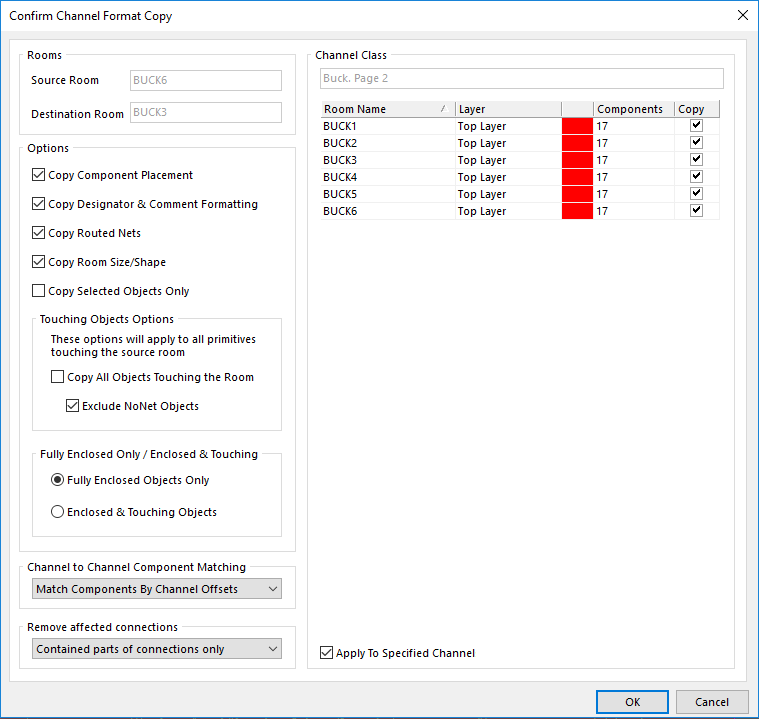

- デザインを行く->部屋->コープルームの形式

- Altiumは、 Choose source roomの下に表示されます。つまり、私の場合はBUCK6で、すべてをコピーする必要がある部屋に突入することを提案します。

- これで、AltiumはChooseDestination Roomを要求します。つまり、レイアウトのコピー先の部屋に突入するように要求します。 いずれかのBUCKを選択します。

- メニューが開き、[ 指定したチャンネルに適用]チェックボックスをオンにすると、選択した部屋だけでなく、同様の部屋すべてにコピーする必要があることがわかります。

- [OK]をクリックしてお楽しみください!

私は一匹も入れずに2つのチャンネルをクリックしました。 たとえば、すべてのチャネルが同一ではない場合があります。 CPUのマザーボード上のVRMを思い出してください。多くの場合、一方には3〜4フェーズ、もう一方には3〜4フェーズがあります。 私の場合、1つの配線で3つのフェーズがあり、別の配線でさらに3つのフェーズがあります。 一般的なイデオロギーは理解できると思います。 結果を見てみましょう:

3つの同一のチャネルを観察し、最も重要な点として、1と同じようにすべてのチャネルに時間を費やしました。この抽象的なケースでは、6倍の時間を節約できますが、実際の問題では人件費を削減する手順はほぼ同じです。 それは重要な要素ではありません-手で6チャンネルを行うと、同じ種類の作業のために「目がぼやける」ため、ミスをしたりレイアウトカーブを作成したりする可能性があります。

まとめ

エレクトロニクス設計の基本的なパラダイムの1つについて学び、自分自身にとって新しく有用なものを学ぶことに興味を持っていたことを願っています。 また、ドキュメント、ライブラリ、およびCADでの適切なツールの使用が正確であれば、エラーを回避して時間を大幅に節約できます。