FizzBuzzテストは、1から100までの数字を生成するプログラムを作成します。3の倍数は「Fizz」という単語に、5の倍数は「Buzz」という単語に、15の倍数は「FizzBuzz」に置き換えられます。 このようなプログラムは数行のコードで実装されているため、インタビューの際に、プログラミングの方法がまったくわからない人を除外することがよくあります。

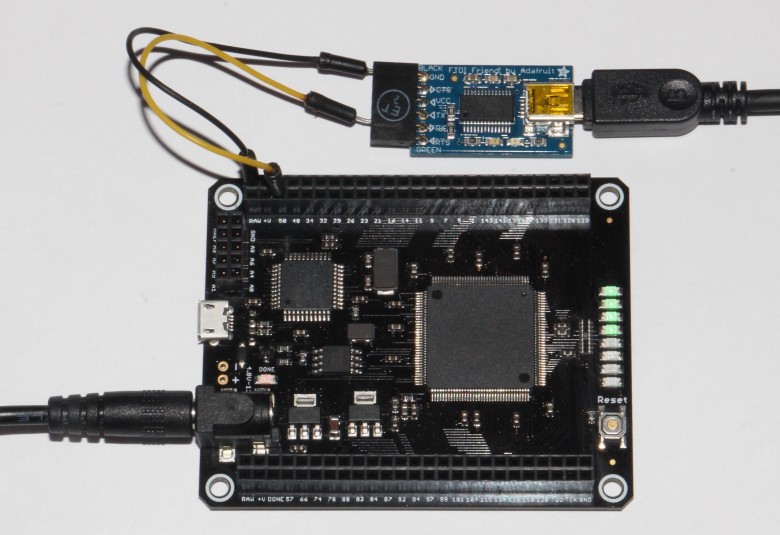

シリアル-USBポートに接続されたMojo FPGAボード。 ボード上の大きなチップはSpartan 6 FPGAです。

FizzBuzzをコードではなくデジタルロジックに実装するのは無意味ですが、学ぶには良い例のように思えました。 1 このプロジェクトでは、初心者向けにシンプルなMojo V3 FPGA開発ボードを使用しました。 ザイリンクスのSpartan 6ファミリのFPGAがインストールされており、これは最小のFPGAの1つですが、9,000のロジックセルと11,000のトリガーを備えているため、多くのことが可能です。

FPGAシリアル出力

FPGAにFizzBuzzを実装するとはどういう意味ですか? これは、ボードからの汎用入出力インターフェース(GPIO)の接点を何にでも接続できることを意味します。そのため、FizzBuzz出力は、LED、7セグメントインジケーター、LCD、VGAモニターなどのさまざまな形式で表示されます。 シリアルチャネルを介した端末へのテキスト出力は、「標準」のFizzBuzzプログラムの精神と最も一致していると判断しました。 したがって、最初にすることは、シリアル出力をFPGAに実装することです。

シリアル通信の基本的な考え方は、ビットを1つずつ送信することです。 RS-232シリアルポートは、1960年にテレタイプとモデムを接続するために考案された、シリアルデータ送信用のシンプルなプロトコルです。 以下の図は、「F」文字(バイナリ01000110)がチャネルを介して順次送信される方法を示しています。 最初に、文字の開始を示す開始ビット(ゼロ)が送信されます。 2 次に、文字の8ビットが逆の順序で送信されます。 最後に、ストップビットが送信されます。 文字間では、バーは次の文字が送信されるまで待機モード(1)のままです。 9600ボーの伝送速度では、各ビットの伝送には1/9600秒かかります。 パリティビットと1ストップビットのない8データビットを使用するこのプロトコルは、8N1として知られています。 シリアルデータ転送には多くのプロトコルがありますが、9600 8N1は非常に一般的です。

「F」文字の9600ボー/ 8N1シリアル伝送

このシリアル伝送を実装する最初のステップは、各ビットに1/9600秒間隔を作成することです。 この間隔は、Mojoごとに5208クロックパルスをカウントすることで測定されます。 3 0〜5207を定期的にカウントするための13ビットカウンターを作成しました。単純なステートマシンは、各インターバルで出力されるビットを追跡します。 スタートビットで開始し、8データビットとストップビットを処理するときに状態を変更します。 状態は4ビットレジスタに格納されます(一般に、FPGAでは、多数のクロックパルス、カウンター、およびステートマシンを処理する必要があります)。

FPGAで間隔および状態レジスタを作成するために、Verilogハードウェア記述言語でコードを記述しました。 Verilogの詳細は説明しません。どのように機能するかを理解してください。 次のコードでは、最初の行で13ビット

counter

レジスタと4ビット

state

レジスタを指定しています。 カウンターは5207に増分され、その後0にリセットされますが、

state

1ずつ増分されて次の出力ビットを処理します。 (

<=

は比較演算子ではなく代入演算子であることに注意してください4 )

always @(posedge clk)

は、手続き型ブロックがクロック周波数の正のエッジでトリガーされることを示します。

reg [12:0] counter; reg [3:0] state; always @(posedge clk) begin if (counter < 5207) begin counter <= counter + 1; end else begin counter <= 0; state <= state + 1; end end

これは通常のプログラムコードのように聞こえますが、まったく異なる方法で動作します。 一般的なプログラミング言語では、プログラムは行ごとに実行されるため、通常、操作は順次実行されます。 たとえば、プロセッサは

counter

の値をチェックします。 次に、

counter

1を追加します。 ただし、Verilogにはプロセッサや実行可能プログラムはありません。 代わりに、コードは操作用のハードウェアを作成します。 たとえば、

counter

を増やすには1つの追加スキームが作成され、

state

を増やすには別のスキームが作成されます。 5207との比較のために追加のロジックが作成されます。シリアルプロセッサとは異なり、FPGAはすべてを並列に実行します。 たとえば、FPGAは5207比較を同時に実行し、

counter

増やしてリセットし、各クロックサイクルで

state

を増やします。 このため、高度な並列タスクでは、FPGAはプロセッサよりもはるかに高速になります。

コードの次の部分は、各状態に対応するビットを出力します。 前と同じように、通常のプログラムコードのように見えますが、連続して実行される操作ではなく、ハードウェア回路を生成します。 この場合、コードは論理ゲート(本質的にマルチプレクサ)を作成して、正しい

out

値を選択

out

ます。

case (state) IDLE: out = MARK; // high START: out = SPACE; // low BIT0: out = char1[0]; BIT1: out = char1[1]; ... BIT6: out = char1[6]; STOP: out = MARK; default: out = MARK; endcase

定数を設定し、カウンターを初期化し、各文字の送信を開始および停止するコードがまだありますが、上記のコードは、Verilogがどのように機能するかの一般的なアイデアを提供します。 シリアルデータ出力のすべてのコードはこちらをご覧ください 。

FizzBuzzアルゴリズム

次のステップは、特にシリアルリンクを介して送信するものを決定することです。 ASCII文字で1から100までの数字を変換する方法は? これはマイクロプロセッサでは簡単ですが、デジタルロジックでは困難です。 問題は、2進数を10進数に変換するには10と100で除算する必要があり、除算がバルブに実装するには非常に不便であることです。 使うことにしました

3桁の数字を個別に保存する2進10進カウンター(BCD)。 これにより、カウンターが少し複雑になりました。ノードがカウンター回路に導入されて、9からある方向または別の方向にオーバーフローするときにカウントプロセスが修正されるようにするためです。 しかし、その後、番号の発行を簡素化しました。

3桁のカウンター用のBCDモジュール( ソースコード )を作成しました。 3つの4ビットカウンター

digit2

、

digit1

、および

digit0

ます。

increment

フラグは、カウンターの増加を示します。 通常、

digit0

のみ

digit0

。 しかし、9に達すると0に変わり、

digit1

が増加します。

digit1

も9になると、0になり、

digit2

が増加します。 したがって、000から999までのカウントダウンがあります。

if (increment) begin if (digit0 != 9) begin // Regular increment digit 0 digit0 <= digit0 + 1; end else begin // Carry from digit 0 digit0 <= 0; if (digit1 != 9) begin // Regular increment digit 1 digit1 <= digit1 + 1; end else begin // Carry from digit 1 digit1 <= 0; digit2 <= digit2 + 1; end end end

前と同じように、これは通常のプログラムのように見えるだけですが、実際には、コードは各クロックサイクルで新しい値

digit2

、

digit1

および

digit0

を生成する

digit2

論理ゲートに

digit1

ます。 システムは命令を順番に実行しないため、パフォーマンスは命令の数によって制限されず、バルブを伝播する信号の遅延によってのみ制限されます。

次のタスクは、3と5による除算性をチェックすることです。単純な除算として、残りの除算もマイクロプロセッサで実装するのは簡単ですが、デジタルロジックでは困難です。 組み込みの除算操作はないため、大量のバルブを作成する必要があります。 IDEは残りを分割するためにそれらを合成できますが、それは無味です。 代わりに、3と5で割った残りのカウンターを作成しました。たとえば、mod3は単に0、1、2、0、1、2 ... 5を出力します。

FizzBuzzの最後の部分は、各行を文字ごとに表示するコードです。 プログラムでは、各文字に対して順次出力プロシージャを呼び出すことができます。 しかし、FPGAでは、別のステートマシンを使用して出力に送信される文字を追跡する必要があります。 各桁をASCIIに変換するとき、バイナリ11はわずかに奇妙な

2'b11

構文を使用して連結されることに注意してください。 ここに記載されているコードは少し単純化されています。 完全なコードには、先頭にゼロのチェックが含まれているため、「001」は「1」として出力されます。

state <= state + 1; // Different state from serial if (mod3 == 0 && mod5 != 0) begin // Fizz case (state) 1: char <= "F"; 2: char <= "i"; 3: char <= "z"; 4: char <= "z"; 5: char <= "\r"; 6: begin char <= "\n"; state <= NEXT; // Done with output line end endcase end else if (mod3 != 0 && mod5 == 0) begin ... Buzz case omitted ... end else if (mod3 == 0 && mod5 == 0) begin ... Fizzbuzz case omitted ... end else begin // No divisors; output the digits of the number. case (state) 1: char <= {2'b11, digit2[3:0]}; 2: char <= {2'b11, digit1[3:0]}; 3: char <= {2'b11, digit0[3:0]}; 4: char <= "\r"; 5: begin char <= "\n"; state <= NEXT; end endcase end

すべてをまとめると、最終的なFizzBuzzスキームは多数のステートマシンとカウンターで構成されます。 メインステートマシンは上記のコードを制御し、文字列の文字を移動します。 シンボルごとに、ステートマシンはシリアル出力モジュールをアクティブにし、シンボルの出力を待ちます。 モジュール内で、ステートマシンはシンボルの各ビットを通過します。 ボーメーターがビット幅をカウントするまで待機します。 シンボル転送が完了すると、シリアル出力モジュールはメインステートマシンに信号を送信します。 それから彼はその行の次のキャラクターに行きます。 ラインが完了すると、メインステートマシンはBCDカウンター(1から100までカウント)をインクリメントし、次のラインの出力を開始します。

プログラミング言語では、順次操作、ループ、サブルーチン呼び出しなどを簡単に実行できます。 しかし、FPGAでは、ステートマシンとカウンターを使用して、何が起こっているかを明示的に追跡する必要があります。 その代わりに、FPGAは強力な並行性と制御を提供します。

FPGAでFizzBuzzを実行する

Verilogコードをコンパイルするには、Xilinx ISEツールを使用しました(以下を参照)。 この開発環境では、コードを記述してシミュレートし、FPGAにロードするための論理回路を合成できます。 ISEツールは非常に単純で、Mojoチュートリアルで説明されています。 合成プロセスはコンパイルよりもはるかに遅くなります。私のFizzBuzzプログラムの場合、約45秒かかりました。

ザイリンクスISEツールでVerilogコードを記述することにより、FPGA機能をプログラムできます。

シミュレーター7でコードが機能したら 、USBケーブル経由でFPGAボードにダウンロードしました。 FPGA出力ピンをUSB-to-serial 6アダプターに接続しました 端末エミュレータ(

screen

)を使用して、コンピューターにシリアル出力を表示しました。 Mojoボードのリセットボタンをクリックしました-(少し余分にデバッグした後)FizzBuzz出力が表示されました(下)。

ターミナルエミュレーターでのFizzBuzz FPGA出力の最初のページ

下の画像は、FPGAを使用した生のシリアル出力データを示しています(黄色)。 これは、FPGAボード上のFizzBuzz回路の最終結果であるパルス列です。 オシロスコープには、復号化されたASCII文字(緑色)も表示されます。 画像では、2、3、および4のFizzBuzz出力(CRおよびLFは復帰および改行文字です)。

FizzBuzz出力の開始時のシリアルデータ出力信号(黄色)。 ASCIIのデコード-緑

FPGA内部では何が起こりますか?

Verilog回路の記述をデジタルロジックに変換する方法と、FPGAがこのロジックをどのように実装するかを尋ねることができます。 ISE合成ツールは、Verilog記述を使用して、FPGA内での実装に適した回路を生成します。 まず、Verilogコードから「ネットリスト」を合成し、ロジックと接続を定義します。 次に、特定のチップ(この場合はSpartan 6)の機能に従って、リストをFPGAプリミティブに変換します。 最後に、信号経路を最小化するための最適化手順が開始されます。

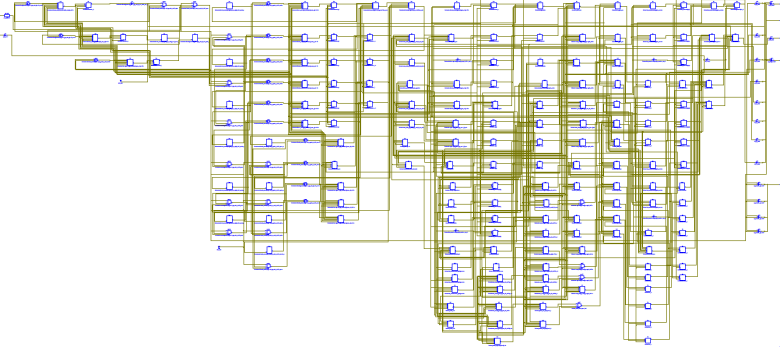

FizzBuzz回路図

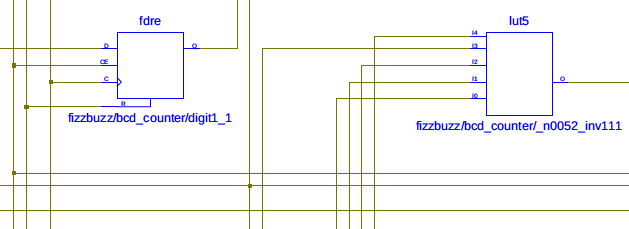

上の図は、合成ツールによって生成された形式のFizzBuzzチェーンを示しています。 ご覧のとおり、Verilogコードは大きなスキームのボールに変わります。 各ブロックは、トリガー、論理要素、マルチプレクサ、またはその他の要素です。 ブロックは、カウンター、状態レジスター、およびFizzBuzzロジックで構成されています。 ロジックエレメントは多数あるように見えますが、実際に使用されているチップ電力は2%未満です。 クローズアップ(下)はトリガーダイアグラム(「fdre」というラベル)を示しています8 BCDカウンターからのルックアップテーブル(「lut5」というラベル)。 Verilogで便利なのは、高レベルで回路を設計することです-そして、それは低レベルの回路に変わります。 これはRTL( レジスタ転送レベル )と呼ばれ、低レベルのハードウェア実装を気にせずにレジスタとそれらに高レベルの操作を適用できます。 たとえば、

count + 1

と記述するだけで、バイナリ加算回路を取得できます。

詳細なトリガーと検索テーブルの図

FPGAは、論理式に興味深い手法を使用しています。 個々のゲートをリンクする代わりに、ルックアップテーブル(LUT)が使用されます。これにより、任意のロジックを実装するのに便利です。 各テーブルには6つの入力ラインがあるため、6つの入力信号で任意の組み合わせロジックを実装できます。 入力信号と64ビットの真理値表の64の異なる組み合わせが判明しました。 このテーブルを64ビットイメージとして保存すると、LUTは任意の論理関数を実装できます。

たとえば、出力ピンのロジックの一部は、以下のロジック回路と同等です。 ルックアップテーブルに

FFFFA8FFFFA8A8A8

64ビット値を格納することで実装されます。 Spartan 6チップでは、このLUTは64ビットのスタティックRAMにあり、FPGAの初期化中にロードされます。 チップには5720の個別のテーブルがあるため、多くの任意のスキームを実装するようにプログラムできます。

FPGAの単一のルックアップテーブルによって実装されるロジックエレメント

タスクの最後の部分は、回路をランダムに接続するマトリックススイッチです。 Spartan 6では、複数のLUT、トリガー、マルチプレクサが構成可能なロジックブロック (CLB)に組み込まれています 9 。 以下に示すように、これらのCLBはマトリックススイッチで接続されています。 各マトリックススイッチブロックは異なるバスを接続するようにプログラムされているため、FPGA接点を自由に配置できます。 FPGA合成プロセスの重要な部分は、配線距離を最小化するためのブロックの配置です。 これは、信号の伝播遅延を最小限に抑えるため、および相互接続パスの予備を保持するために必要です。

Spartan 6 FPGAマトリックススイッチャーでは、CLB間の任意の接続が可能です。 ユーザーマニュアルから

FPGAを試すべきですか?

個人的には、最初はFPGAに不安を感じました。なぜなら、それらは怖くて奇妙に思えたからです。 学習曲線はありますが、FPGAは思ったほど複雑ではありません。 新しいプログラミングパラダイムに興味がある場合、FPGAは異なる角度から物事を表示します。 シーケンシャル操作など、当然のことと思われるものが前面に出てきます。 高い同時実行性を試すことができます。 また、FPGAを使用すると、デジタル回路の動作をよりよく理解できます。

ただし、LED /スイッチの接続に少なくとも少し慣れておらず、基本的なデジタルロジック(バルブ、トリガー、ステートマシン)を理解していない場合は、FPGAの実験をお勧めしません。 しかし、Arduinoに慣れているのであれば、FPGAは賢い次のステップです。

おそらく、ほとんどのアプリケーションでは、マイクロコントローラーはFPGAよりも優れており、プログラミングが簡単です。 高いデータレートや同時実行性が必要ない場合、FPGAはおそらく冗長になります。 私の場合、マイクロコントローラーは3メガビットイーサネットゲートウェイにほとんど対応していなかったため、次のプロジェクトではFPGAを検討します。

Mojoは最初から良いボードですか?

Mojo FPGA開発ボードはAdafruitとSparkfunから販売されているので、ハッカーにとって良い選択だと思いました。 このボードはFPGAプログラミングの初心者向けに設計されており、この役割にうまく対応しています。 Mojoの作成者は、Verilogチュートリアルの大規模なコレクションを作成しました。 10 。 マニュアルが特定のボード向けに書かれている場合、ボードとツールの問題をより迅速に解決できます。 Mojoは標準のUSBケーブルでプログラムされています-特別なJTAGアダプターよりも便利です。

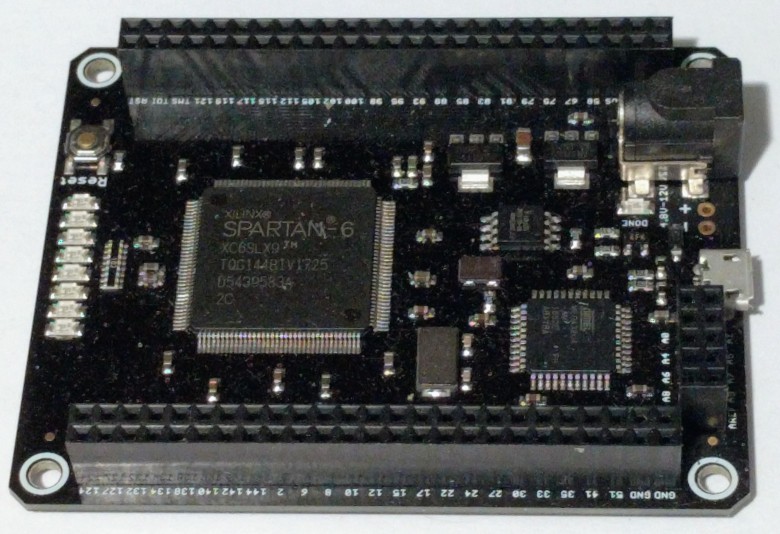

Spartan-6 FPGAチップを搭載したMojo FPGA

Mojoには多くのI / Oピンがありますが、8個のLEDを除き、周辺機器は販売されていません。 ボタン、7セグメントディスプレイ、VGA出力、センサーなどがある場合は、ボードで実験する方が快適です。 (Mojoに接続するのは難しくありませんが、Mojoを含めると便利です)。 さらに、一部の開発ボードには外部RAMがありますが、Mojoにはありません。 これは、大量のメモリを必要とするロジックアナライザーなどのアプリケーションの問題です。 11 (ただし、MojoはIO パッドまたはRAMパッドで拡張できます)。

Mojoを使い始めるのに適した本は、 FPGAプログラミングです。 また、はるかに安価なマザーボードPapilo OneおよびElbert 2についても説明しています。 他のオプションをご覧になりたい場合は、 FPGA開発ボードのリストをご覧ください。

おわりに

FizzBuzzタスクはFPGAに実装するのは実用的ではありませんが、興味深いことに、FPGAプログラミングについて多くのことを学びました。 しかし、もちろん、彼らがFizzBuzzにインタビューを頼むと、私は仕事に就きません! 私のコードはGitHubにありますが、私はまだこのビジネスを始めたばかりです。

メモとリンク

1. FPGAにマイクロプロセッサを実装するのは簡単な作業です。 たとえば、Spartan 6チップでは、IDEウィザードのいくつかのボタンを押すことができます 。これにより、MicroBlazeプロセッサ用の回路が生成されます 。 したがって、頭のいい人はCの数行でFizzBuzzコードを書き、それをFPGA内のプロセッサーで実行します。 しかし、私にとっては簡単すぎます。 ↑

2.開始ビットが必要です。そうしないと、文字の最初のビットが1の場合、レシーバーは文字の始まりを判別できません。 ↑

3. Mojoのクロック周波数は50 MHzであるため、9600ボーの場合、各ビットには最大50,000,000 / 9,600、つまり約5,208クロックサイクルかかります。 これは非常に高速ではないため、実験ではコードを1000万ボーの速度で実行しました(各ビットで最大5クロックサイクルをカウントします)-そして回路は生き残りました(USB-シリアルインターフェースは230400ボーまでの速度しかサポートしないため、結果を確認しましたオシロスコープで)。 ↑

4. Verilogでは、

<=

は非ブロッキング割り当て演算子であり、

=

はブロッキング割り当て演算子です。 ノンブロッキング割り当ては並行して発生し、通常はシーケンシャルロジック(クロックトリガー)に使用されます。 ブロック割り当ては、組み合わせロジック(クロックなし)に使用されます。 これは少しわかりにくいです。詳細はこちらをご覧ください。 ↑

5. 2進数ではなく2進数10進数のカウンターを使用したため、5で除算した残りの部分は、最後の桁を見てほぼ自明に決定されます。 しかし、3で除算することの残りは些細なことではないので、オプションをカウンターのままにしておく必要がありました。 ↑

6.シリアルポートがないため、シリアル入力をコンピュータに直接送ることはできませんでした。 代わりに、 USB-シリアルアダプター 、AdafruitのFTDI Friendを使用しました。 このアダプタは、元のRS-232の不快な+/- 15ボルトとは異なり、3.3ボルトの信号も受信できます。 ↑

7. FPGAのデバッグは、プログラムのデバッグとはまったく異なります。 FPGAは本質的にブラックボックスであるため、最初にシミュレータですべてを確認する必要があります。そうしないと、LEDが点滅して「FPGA-hell」になり、何が起こっているのかを理解しようとします。デバッグのプロセスで、回路をシミュレートするには、「テストベンチ」-Verilogコードを作成する必要があります。Verilogコードは、異なる時間に異なる入力データを提供します(例)。次に、シミュレーター(下記)を実行し、出力が正しいことを確認します。ザイリンクスISimシミュレーターを使用すると、FPGA回路をチェックでき、問題が発生した場合は、シミュレーターを使用して内部信号を調べて問題を特定できます。実際のFPGAで実行しているときにシミュレータで完全にテストした後、私のコードには最も些細な問題しかありません。主なものは、間違った連絡先にシリアル出力を割り当てたため、出力がなかったことです。

↑

8. Spartan 6 FPGAは、いくつかのタイプのトリガーをサポートしています。FDREは、同期リセット/セット入力およびクロック操作を備えたDトリガーです。 ↑

9. Spartan 6 FPGA(CLB)の構成可能なロジックブロックは非常に複雑です。 LUTモジュール、8つのトリガー、ワイドマルチプレクサー、ロジック、分散RAM、およびシフトレジスタが含まれています。これらのブロックのコンポーネントを堅くはんだ付けすると、柔軟性がわずかに低下しますが、マトリックススイッチの設計は大幅に簡素化されます。 CLBの詳細については、CLB ユーザーガイドを参照してください。 Spartan 6 FPGAには、18×18ビットをすばやく乗算できるクロックブロックやDSPブロックなど、他のタイプのブロックがあります。 ↑

10. Verilogの代わりにVHDLがあります。これは開発環境でもサポートされています。Mojo は、Mojoチームが開発したよりシンプルなFPGA言語であるLucidもサポートしています。Mojo のLucidガイドが言語を説明し、そのテーマに関する本があります。ただし、Lucidよりも標準言語を学ぶ方が良いと判断しました。 ↑

11. Mojoには外部RAMはありませんが、576キロビットの内部メモリがあります。これは、メガバイトの外部DRAMを搭載したボードと比べるとごくわずかです。 ↑