Habrの読者には、電子機器の開発のために「標準ではない」タイプのメモリを使用し続けています。 前回、ハイブリッドメモリキューブ(HMC)とFPGAへの接続について説明しましたが、この記事では、比較的最近、2014年に市場に登場したサイプレスのHyperBusインターフェイスを備えたメモリチップに焦点を当てます。

HyperRAMとHyperFLASHの2種類のデバイスが利用可能になりました。 HyperRAMは擬似静的メモリ(DRAM + 1チップの充電方式)で、HyperFLASHはHyperBUSインターフェイスを備えたNORフラッシュメモリです。 2-in-1コンボチップも利用可能です:HyperFLASH 512Mb + HyperRAM 64Mb。 最新のソリューションの価値は、信号数が少なく、設置面積が小さく、十分に高速で適切な価格であることです。

たとえば、サイプレス(HyperBUSのメインプロモーター)が、コントローラーを中心に、車載電子機器でこれらの次世代メモリチップをどのように見ているかを以下に示します。

つまり、サイプレスはすべての外部メモリを1つのチップに置き換えることを提案しています。 また、一般的に、この提案は、特にボードサイズの要件が厳しいプロジェクトでは根拠がありません。

SRAM、DRAM、および従来のFLASHと比較して多くの利点がありますが、HyperBUSソリューションの普及は、最近まで-昨年-サイプレスの1つのマイクロコントローラー(もちろんFPGA)だけでサポートされていたため、まだ行われていません。 現在、ビジネスは前進しており、ますます多くのマイクロコントローラーがサポートを提供しています。

2週間前の2017年12月5日に、サイプレスはxSPI(eXpanded SPI)標準にHyperBusメモリインターフェイスを含めることを発表しました。これは、半導体技術標準化委員会であるJEDECによって調整されます。 xSPI規格では、高性能シリアルインターフェイスの互換性要件が定義されているため、コントローラーおよびチップセットのメーカーはユニバーサルメモリコントローラーを開発できます。 JEDEC xSPI規格にHyperBusインターフェイスを含めると、HyperBusに基づくメモリの設計が簡素化され、自動車、産業オートメーション、IoT(モノのインターネット)向けの電子機器を開発する際に、インスタントオン(インスタントオン)の機能をより柔軟に実装できるようになります。

HyperBusメモリインターフェイスを備えたチップは非常に有望であり、私たちのプロジェクトの1つでそれらの使用の経験を共有することを急いでいます。

タスクの説明

インターフェースに関する話に進む前に、どのタスクで適用されたかを説明しましょう。 次の開発では、最小限のレイテンシと十分に大きい帯域幅で外部デバイスにデータ出力を提供する必要がありました。 同時に、ボード上のスペースはあまりなく、完全になくなっています。 Linuxを搭載したプロセッサをマッチボックスのサイズのスカーフに搭載し、適切なバンドル、USBコントローラ、メモリに実際にアクセスしてデータを送信するFPGA、およびその他の特定のスタッフィングを取り付ける必要がありました。 当然、すべてのコンポーネントは厳密な選択を経ました。

その結果、メモリチップの選択はHyperRAMに委ねられました。 パラメーター:FPGAに接続するための信号の数-12; 最大レイテンシ-36 ns; 帯域幅-333 MB / s; ボリューム-8 MB; エンクロージャ— 6x8x1.2 mm TF-BGA。

比較のために、同じボリュームのSRAMには35行、SDRAMなどが必要です。 この場合、SRAMのコストはHyperRAMよりも1桁高くなり、SDRAMのトレーサの多大な努力が必要になり、プリント回路基板のコストが大幅に増加します。

レイテンシを最小限に抑えるための要件により、サードパーティ開発者の高レベルIPモジュール(パイプライン処理とスケジューリングを備えたAVALON <-> HyperBusなど)を使用できませんでした。 その結果、私たちのタスクは、HyperRAMを操作するための専用IPモジュールを開発することでした。

このモジュールは、DevMA HyperMAXデバッグボードで開発されました。 ボードには、2つの興味深いデバイスが含まれています。HyperRAMとISSIのHyperFLASHです。 さらに、このボードには、自動車の電子機器で使用するためのさまざまなパンが詰め込まれています。

市場で入手可能なIPモジュールは、AXI4およびAVALONインターフェイスを介したHyperBUSとの連携をサポートし、HyperFLASHから直接ソフトウェアプロセッサプログラムを実行する機能も宣言していることに注意してください[ たとえば ]。

HyperMAX(リビジョン1.1)のデバッグに関するいくつかの言葉

プロジェクトの例は非常に平凡です。 動作周波数を選択するための理解できないロジックを備えた一般的なHyperRAMのプロジェクト。 RWDSに定数を登録する代わりに、固定信号遅延が入力バッファーに設定され、HyperRAMは116 MHzの周波数でシャーマニックに動作します。 DDR信号は、SDRバッファーを使用して入力ピンに配線されます。 穴はコネクタの近くに配置されるため、スタンドにナットをねじ込むことはできません。 コネクタの1つでは、スキームに従ってGPIO信号がピンに出力されますが、実際には存在しません。 そして、我々はまだこれを確認していません。 一般に、ドイツ人がHyperMAXボードを開発し、300ユーロ以下の費用がかかるという事実にもかかわらず、デバッグは湿っています。 しかし、彼らが言うように、「選択のすべての富で、他の選択肢はありません」。

次に、HyperRAMチップの動作について説明します。 HyperFLASHとの相互作用は同様の方法で構成されていますが、いくつかの単純化が行われています。

HyperRAM

HyperRAMチップは、再充電メカニズムが組み込まれたHyperBUSインターフェース上で動作する高速DRAM-CMOSメモリです。 再充電回路は、読み取り/書き込み操作が実行されていないときに機能します。 その結果、ホストの観点から見ると、メモリは静的に見え、擬似静的メモリ(PSRAM)と呼ばれます。

HyperBusは、少数の信号を使用する場合に高い読み取り/書き込み速度を実現できるDDRインターフェイスです。 データは、サイクルごとに16ビットワードの8ビットバスで送信されます。 すべてのラインはLV-CMOS互換です。 これらのデバイスは、1.8 Vと3.0 Vの2つのバージョンの供給電圧で利用できます。

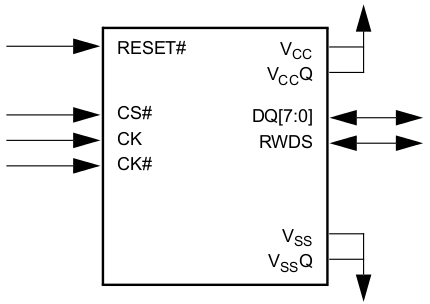

仕様によれば、HyperBUSインターフェースには必須およびオプションの信号が含まれています。

主要なHyperBUSインターフェース信号

私たちの場合、必須のもののみが使用されました(上の図を参照)。

- CS# -デバイス選択信号。 チップ選択信号の存在により、同じバス上の複数のデバイスをマスタースレーブアーキテクチャと組み合わせることができます。

- CK / CK# -同期信号。 3 Vの電圧で駆動するデバイスは、最大166 MHzの周波数の差動ペアCK / CK#により、1.8 Vの電源で、100 MHz以下の周波数で1つのCKラインで同期されます。

- DQ [7:0] -双方向データバス。

- RWDS-多機能の双方向信号(リードワイヤデータストローブ)。

RWDS信号は、次の機能を実行します。

- トランザクションの開始時に、メモリがロードされ、データを発行/記録する前に必要なレイテンシを示します:0-一度限りの遅延。 1-二重遅延(初期読み取り/書き込み遅延)。

- 書き込みトランザクションでは、データを発行するプロセスはホストによって駆動され、変更すべきではないバイトをマスクします。

- 読み取りトランザクションでは、データを発行するプロセスはメモリによって駆動され、データを同期します(ソース同期読み取りデータストローブ)。

遅延と同期については以下で説明します。

デバイスとのデータ交換はトランザクションの形式で行われます:マスターがチップセレクトをアサートし、クロック信号を送信し、制御バイトを発行し、数クロックサイクルを期待し、データを交換し、同期を停止し、チップセレクトをディアサートします。

最初の3クロックサイクルで、ホストは6つのトランザクション制御バイト(COMMAND-ADRESSまたはCA )を送信します。 詳細に進むことなく、単にパラメーターをリストします。

- トランザクションタイプ:読み取りまたは書き込み。

- アドレス空間:メモリまたは制御レジスタ。

- 書き込み/読み取りシーケンスのタイプ:線形(線形)またはバースト(バースト)。

- 列と行のメモリアクセスの開始アドレス。

メモリセルはデータ交換トランザクション中に再充電できないため、1つのトランザクションの期間(トランザクション期間)とそれらの間の遅延(初期レイテンシ)に制限が課せられます。

CAの送信と同時に、メモリはRWDSラインにレイテンシインジケータを設定します。記録のためにデータを送信する前、または読み取りのためにデータを受信する前に何クロックサイクル待つ必要があります。 メジャーの数の値については、制御レジスタから学習します。 この値は、クロック周波数に応じてメモリによって個別に決定されます。 RWDSが「0」の場合、必要なメジャー数は1回、「1」の場合は2回と予想されます。 メモリが常に2倍の遅延間隔で実行されるようにデバイスレジスタを設定し、ティックの数をデフォルト値とは異なる値に設定できます(ただし、この値は元の値より小さくすることはできません)。

書き込みトランザクションでは、ホストは必要なクロックサイクル数待機した後、バスに書き込まれるデータを設定します。

書き込みトランザクション

データはクロック信号の両端でそれぞれメモリにキャプチャされ、データは270度シフトされたクロックによって出力DDRレジスタに入力されます。 データ転送中のRWDS信号は、記録中にメモリによって変更されるべきではないバイトをマスクします。 制御レジスタにワードを書き込む場合、遅延なくCAの直後に発行する必要があります。

読み取りトランザクションでは、データはメモリによって公開されます。

読み取りトランザクション

バス上のデータ変更は、RWDS信号の両方のエッジによって同期されます。 また、メモリから出力されるデータは、エッジに沿ったRWDS信号によって同期されることを忘れないでください。 そのため、正しく読み取るには、RWDSを90度シフトする必要があります。

データ信号に対するRWDS信号遅延

データの書き込み/読み取りは、CAで指定されたアドレスから開始されます。 各受信/発行されたワードのアドレスは2ずつ増加します。トランザクションは、チップセレクトのクロックとディアサートが停止した後に終了します。

作品のいくつかの機能に注意してください。 まず、アドレスが最大値を通過すると、未定義の方法でデータの発行/書き込みが開始されます。 したがって、アドレスカウンターをオーバーフローするトランザクションでメモリにアクセスしないでください。 第二に、メモリ要素の定期的な再充電が必要なため、チップはトランザクションの期間を制限します。 最大期間は温度に依存し、仕様に記載されています。 最も深刻なケースでは、166 MHzの速度の1つのトランザクションで、300バイトを少し超えて読み書きできます。

デバイスには、情報と構成の2つのレジスタがあります。 情報レジスタは、製造元とデバイスのタイプ(HyperRAM / HyperFLASH)、デバイスの行、列、および水晶の数に関する情報を提供します。 コンフィギュレーションレジスタを使用すると、出力インピーダンス、データにアクセスするバッチモードでのパケットの長さ、レイテンシのタイプ(定数/変数)を設定できます。また、遅延値を設定し、デバイスを低電力モード(ディープパワーダウン)に設定できます。

一見すると、質問が発生する場合があります。読み取り時にこの遅延が不明な場合、遅延に関する情報を使用して構成レジスタの値を読み取るにはどうすればよいですか。 このためには、データ出力がRWDSラインを介してメモリによって同期されることを考慮する必要があります。 実際、データキャプチャスキームはソース同期であるため、遅延の実際の値はどこにも考慮されません。 また、書き込みトランザクションでは、レイテンシ値とRWDS信号の状態に応じて、データを発行する前にクロックをカウントする必要があります。

次に、構成レジスタの値を解析する例を示します。

結論

一般的に、HyperBUSインターフェースを備えたメモリは、心地よい印象しか残しませんでした。 FPGAでの作業は非常に簡単で、開発されたモジュールはリソース集約型ではありません。 現時点での唯一の欠点は、HyperBUSを備えたマイクロコントローラーの範囲が限られていることです。 したがって、多くのベンダーとのインターフェースのサポートを待ち、将来のプロジェクトで明確に実装します。