ツールチェーンとして、STM8用IAR Embedded Workbenchが無料ライセンスで使用されました(コードサイズの制限は8Kb)。

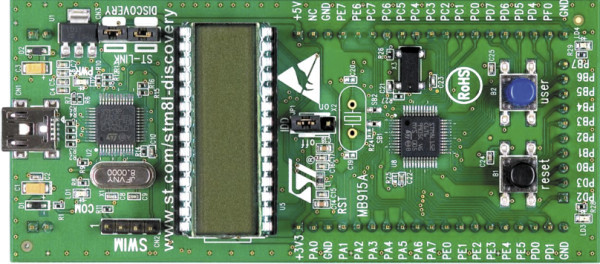

1-Wireバスのハードウェアドライバとして、以前の記事の回路が採用されました。 接続は次のとおりです。

- 評価ボードのピンPB1はOCRAドライバーに接続されています

- 評価ボードのPD0ピンはICPドライバーに接続されています

- 評価ボードのピンPA5はPULLUPドライバーに接続されています

GND、電源+ 5V、および電源+ 3V3を接続することを忘れないでください。

AVRとは異なり、STM8(およびSTM32)マイクロコントローラーは、広範囲の内部周辺機器を提供します。 したがって、説明されているプロジェクトはいくつかの方法でコンパイルできます。

- IRQのみ。 作業のロジックは、DMAを使用せず、割り込みによってのみ実装されます。 このオプションは、__ DRV_ONEWIRE_DMAシンボルが定義されていない場合にコンパイルされます。

実装の利点:

- 必要なRAMは3バイトのみ

- タイマーを任意の解像度にプログラムする機能

実装の短所:

- 多数の割り込み(送信ビットごとに3つの割り込み)

- 8ビット伝送のDMA。 タイマーのプログラミングとビットの送受信中の結果の保存は、DMAを使用して行われます。 このオプションは、シンボルが__DRV_ONEWIRE_DMA = 1の場合にコンパイルされます。

実装の利点:

- 9バイトのRAMが必要

- 少数の割り込み(最初に送信されたビットごとに1つの割り込みと、交換が正常に完了した場合は3つの割り込み)

実装の短所:

- 高解像度のためにタイマーをプログラムできない

- 16ビット伝送のDMA。 ビットの受信および送信中のタイマーのプログラミングと結果の保存は、DMAを使用して行われますこのオプションは、シンボル__DRV_ONEWIRE_DMA = 2のときにコンパイルされます。

実装の利点:

- 少数の割り込み(最初に送信されたビットごとに1つの割り込みと、交換が正常に完了した場合は3つの割り込み)

- タイマーを任意の解像度にプログラムする機能

実装の短所:

- 17バイトのRAMが必要

さらに、PWM禁止入力タイマー(BREAK信号)が存在するため、アクティブプルアップがオンになっているときにデータを交換しようとする試みに対してハードウェアベースの保護を実装することが可能になりました(つまり、1ワイヤが誤って地面に短絡しないようにするため)変換を実行するために電源が供給されます)。

一般的な実装機能

プリミティブが使用されていない場合、出力信号PB1は低信号レベルを維持します(つまり、変調ステージはアクティブではありません)。 タイマーは、期間がタイムスロットの持続時間にビット間の保護休止の長さ(ビット転送手順の場合)または合計RESETパルス持続時間、PRESENCEの可能な開始までの休止、およびPRESENCE自体の最大持続時間(RESETプロシージャの場合)に対応するようにプログラムされます。

制御レジスタPWM(TIMx_CCR1)およびキャプチャ(TIMx_CCR2)は、シャドウレジスタを使用するようにプログラムされています。 つまり、PWMレジスタ((TIMx_CCR1)のプログラム変更後、その値は、マイクロコントローラー内にUEV信号が表示された後にのみ使用されます。この信号は、カウンターが指定のピーク(周期)に達すると自動的に生成されるか、TIMx_EGRレジスタのUGビットを設定することで生成されます) 。

PWMを開始する直前に、最小送信ビットの必要なパルス幅が計算され、PWMレジスタ(TIMx_CCR1)にロードされます。 その後、TIMx_CR1レジスタのCENビットを設定して、タイマーを開始します。 この時点では、PWM信号はまだアクティブではありません。 TIMn_BKRレジスタのMOEビットは以前0にリセットされていました。その後、UGビットはプログラムでTIMx_EGRに設定され、内部UEV信号がアクティブになり、現在のカウンタ値が0にリセットされ、PWMレジスタ(TIMx_CCR1)の内容が比較に使用されるシャドウコピーにロードされます。

さらに、AOEビットは以前にTIMn_BKRレジスタで設定されていたため、TIMn_BKRレジスタのMOEビットはUEV信号によって自動的に設定され、PWM出力が有効になります。 ただし、これは、外部アクティブプルアップ制御から生成されるBREAK信号が生成されない場合にのみ発生します(これは、入力モードまたは出力モードにプログラムされているかどうかに関係なく、マイクロコントローラ内のBREAK信号が外部ピンの信号値から直接生成されるため可能です) 。 したがって、RESETプロシージャ中またはビットを送信/受信しようとするときにアクティブプルアップ信号がアクティブな場合、PWM出力の包含はブロックされます。

IRQのみの実装の動作原理は、アップダウンタイマー動作モードの代わりに「指定値まで」のカウントモードが使用されるという違いを除いて、 前の記事で説明したものと同じです。 これは、16ビットタイマーのビットが、1ビットの送信のタイムスロット期間の形成と、「PRESENCE待機を伴うRESET信号の生成」手順の実装の両方に十分であるために可能になりました。

この実装では、前のビットの送信の終了時に発生する割り込みを処理するときに、次のパルスの持続時間の計算が実行されます。

8ビットおよび16ビット伝送でDMAを使用する実装は基本的に同じで、PWMとICPのビット深度のみが異なります。 すべてのパルス持続時間は、タイマーが開始する前に事前に計算されます。 最下位ビットのパルス幅は上記のようにPWMレジスタ(TIMx_CCR1)にロードされ、残りの値をロードするために、必要に応じて、最初のDMAチャネルがプログラムされます。 すべての測定結果は、常に2番目のDMAチャネルを使用して保存されます。

生成されたコードはIARの無料ライセンスの制限内に十分収まっているため、評価ボードを手元に置いて、すぐに実験を開始できます。 また、ハードウェアデバッグの可能性のおかげで、マイクロコントローラー周辺の機能の特徴を調べることもできます。

ご注意

ソースコードには、1-Wireバスに交換プロトコルを実装するためのいくつかの高レベルの手順があります。 これらは非常に機能していますが、条件付きコンパイルディレクティブによってプロジェクトから除外されています。 プロトコルの高レベル部分のpthreadと非同期実装の使用を楽しみにしています。

参照: