ご挨拶!

前回、 DMAをFPGAに引き上げることに決めました。

今日、FPGAにプリミティブLCDコントローラーを実装し、このコントローラーで動作するフレームバッファードライバーを作成します。

FPGA向けの開発とLinux向けドライバーの作成が非常に簡単ですが、興味深いことをもう一度確認します。

また、最後に小さな世論調査があります-私はコミュニティの意見を知りたいです。 難しくなければ、投票してください。

そのため、 Cyclone V上のHPSには統合グラフィックスコントローラーがありません。 ディスプレイなしでは生きていけません- 測定結果はどこで入手できますか?

もちろん、フレームバッファのソフトウェア実装(deferred_ioとダブルバッファリングの形であらゆる種類の有用性が追加されている)を使用することでのみ対応できます。 しかし、これはすべて同じですが、それほど速くはなく、確かに私たちが選んだものほど興味深いものではありません。

そして、FPGAで非常にシンプルでありながら完全に機能するLCDコントローラーの実装を選択します。これにより、ディスプレイにデータを書き込むという形でCPUから不要な負荷が取り除かれます。

ILI9341チップに基づいたLCDを使用します。

したがって、今日の計画:

- 建築について考える

- 私たちはLCDを研究しています

- Linuxドライバーの作成

- FPGAでモジュールを開発します

- U-bootで何かを構成する

- デバッグ

建築

Linux フレームバッファーとは何ですか?

簡単に言えば、これは単なるメモリ領域であり、ディスプレイに記録されるディスプレイにつながる記録です。

ユーザースペースからのアクセスは、デバイスファイル/ dev / fb [N]を介して行われます。

通常、標準システムコールが実装されています-open()、close()、read()、write()、lseek()、およびmmap()。

ドライバーでは、ほとんどの関数が1つのタスクを実行します。これは、メモリに保存されているフレームを更新することです。

ハードウェアに実装されていない場合、メモリからLCDにデータをコピーする機能もあります。

すべての構造と機能については、これらの記事( リンク1回とリンク2)で詳しく説明されています。

情報を複製しても意味がないため、アーキテクチャに影響を与えるもののみを分析します。

そのため、メモリ内のデータを更新するように設計されたいくつかの関数があります。 彼らはわずかに異なる署名を持っています。 これらの関数を使用すると、フレーム全体と数ピクセルのみを再描画できます。

フレームを更新した後、LCDに分類する必要があります。 当然、フレームの変更された部分のみをコピーするには、より少ないデータの転送が必要です。 また、CPUを使用してデータをコピーした場合、これを考慮する必要があります。

ただし、コピーはFPGAのDMAコントローラーによって実行されるため、これについて心配することはなく、フレーム全体を再描画します。

次の質問は、いつフレームを再描画するかです。 簡単な解決策の1つは、同期的に、つまりメモリ内のデータを更新する各関数の最後にレンダリングを実行することです。 これは、mmap()を使用する場合を除き、すべての場合に有効です。

マッピングを実行した後、ユーザー空間プロセスがメモリの内容を変更した時期を判断するのはそれほど簡単ではありません。 この問題はdeferred_ioで解決できます(同時に、更新され再描画が必要な特定のメモリページを定義します)。 しかし、実装はできるだけシンプルで簡単なものにする必要があるため、別の方法で行います。

FPGAのコントローラーは、n FPSの周波数でフレーム全体をレンダリングします。 そして、ドライバー関数でメモリを更新することに関して、これを非同期的に行います。 したがって、ドライバーで行う必要があるのは、LCDとFPGAコントローラーの初期化だけです。 そして、実装する必要のないフレームバッファメモリにデータを書き込んでも、このための標準機能がすでにあります。

FPGAのコントローラーも非常にシンプルです。 彼の仕事:

- fpga2sdramまたはfpga2hpsインターフェイスを使用して、指定された領域からデータを読み取ります

- 読み取りデータをLCDに転送し、必要なトランザクションを形成します

- CPUがLCDを介してインターフェースに直接アクセスできるようにします

- 指定されたFPSを発行する

LCDの説明

LCDについて知る必要があるのは、LCDを初期化する方法と、書き込みトランザクションがどのように見えるかだけです。

ドライバーに到達したときに初期化を検討し、トランザクションを調べます。

FPGA(データ転送用)とドライバー(ディスプレイ設定用)の両方に実装する必要があります。

ILI9341は複数のインターフェイスをサポートしています。 私は8080と呼ばれるIntelのプロセッサーの名前で最初に登場した16ビットのパラレルインターフェイスを使用します。 信号は次のとおりです(最初はより一般的な名前が示され、括弧内はILI9341のデータシートからの名前です)。

- CS(CSX)-チップ選択、アクティブレベル0。チップを選択するための信号は、地面に巻かれています。

- RST(RESX)-リセット、アクティブレベル0。リセット信号、GPIO HPSで取得しました。

- RS(D / CX)-レジスタ選択。 信号が0の場合、コマンドはDATAバスで発行され、それ以外の場合はデータが発行されます。

- WR(WRX)-ストロボを書き込みます。 ストロボ録音。

- RD(RDX)-読み取りストロボ。 読書ストロボ。

- DATA(D)-RSに応じたデータまたはコマンド。

書き込みトランザクションは非常に簡単です。

書き込みトランザクション

読み取りトランザクションはそれほど複雑ではありませんが、必要ないため、考慮しません。

Linuxドライバー

ドライバーには何がありますか?

まず、FPGAレジスタの読み取り/書き込み用の関数。 私の同僚であるishevchukの 記事で、ステータス制御レジスタとは何か、そしてそれらを使用する方法について詳しく読むことができます。

CSRの読み取り/書き込み機能

static void fpga_write_reg(int reg, u16 val) { iowrite16(val, fpga_regs + 2*reg); } static u16 fpga_read_reg(int reg) { u16 tmp; tmp = ioread16(fpga_regs + 2*reg); return tmp; } static void fpga_set_bit(int reg, int bit) { unsigned long tmp = fpga_read_reg(reg); set_bit(bit, &tmp); fpga_write_reg(reg, tmp); } static void fpga_clear_bit(int reg, int bit) { unsigned long tmp = fpga_read_reg(reg); clear_bit(bit, &tmp); fpga_write_reg(reg, tmp); }

第二に、コマンドとデータをLCDに直接記録する機能。 ディスプレイを初期化するために使用されます。

関数は絶対に「不器用」です-データシートに示されているようにトランザクションを作成してください(この記事ではそれ以上です)。

LCDデータ/コマンド書き込み機能

static void lcd_write_command(u16 val) { /* Write command code */ fpga_write_reg(LCD_DATA_CR, val); /* WR and RS low, RD high */ fpga_write_reg(LCD_CTRL_CR, LCD_CTRL_CR_RD); ndelay(1); /* RS low, WR and RD high */ fpga_write_reg(LCD_CTRL_CR, LCD_CTRL_CR_RD | LCD_CTRL_CR_WR); ndelay(1); /* All control signals high */ fpga_write_reg(LCD_CTRL_CR, LCD_CTRL_CR_RD | LCD_CTRL_CR_WR | LCD_CTRL_CR_RS); } static void lcd_write_data(u16 data) { /* Write data */ fpga_write_reg(LCD_DATA_CR, data); /* WR low, RD and RS high */ fpga_write_reg(LCD_CTRL_CR, LCD_CTRL_CR_RD | LCD_CTRL_CR_RS); ndelay(1); /* All control signals high */ fpga_write_reg(LCD_CTRL_CR, LCD_CTRL_CR_RD | LCD_CTRL_CR_RS | LCD_CTRL_CR_WR); }

実は、単純なLCD初期化です。

LCD初期化機能

static void lcd_init(struct fb_info *info) { // Clear data fpga_write_reg(LCD_DATA_CR, 0); // All control signals high fpga_write_reg(LCD_CTRL_CR, LCD_CTRL_CR_RD | LCD_CTRL_CR_RS | LCD_CTRL_CR_WR); mdelay(100); lcd_write_command(ILI9341_DISPLAY_ON); lcd_write_command(ILI9341_SLEEP_OUT); lcd_write_command(ILI9341_INVERTION_OFF); lcd_write_command(ILI9341_MEM_ACCESS_CTRL); lcd_write_data(MY | MX | MV | BGR); lcd_write_command(ILI9341_PIXEL_FORMAT); lcd_write_data(0x0055); lcd_write_command(ILI9341_COLUMN_ADDR); lcd_write_data(0x0000); lcd_write_data(0x0000); lcd_write_data((DISPLAY_WIDTH-1) >> 8); lcd_write_data((DISPLAY_WIDTH-1) & 0xFF); lcd_write_command(ILI9341_PAGE_ADDR); lcd_write_data(0x0000); lcd_write_data(0x0000); lcd_write_data((DISPLAY_HEIGHT-1) >> 8); lcd_write_data((DISPLAY_HEIGHT-1) & 0xFF); lcd_write_command(ILI9341_MEM_WRITE); }

使用されるコマンドについて簡単に説明します。

ILI9341_DISPLAY_ON(0x29)およびILI9341_SLEEP_OUT(0x11)、これは予想外ですが、ディスプレイをオンにして起動します。

ILI9341_MEM_ACCESS_CTRL(0x36)-これはメモリスキャンの方向の設定です。

ILI9341_PIXEL_FORMAT(0x3a)-画像形式。ピクセルあたり16ビットです。

ILI9341_COLUMN_ADDR(0x2a)およびILI9341_PAGE_ADDR(0x2b)は、ディスプレイの作業領域を設定します。

ILI9341_MEM_WRITE(0x2c)-このコマンドは、データトランザクションが後に続くことを示します。 この場合、現在の位置は、ILI9341_COLUMN_ADDRとILI9341_PAGE_ADDRを使用してそれぞれ設定された初期の列と行に設定されます。 各トランザクションの後、列は自動的に1ずつ増加します。列が最後の列と等しくなると、次の行への遷移が発生します。 列と行の両方が最後に等しくなると、位置は最初の位置に戻ります。

したがって、ILI9341_MEM_WRITEコマンドの後、FPGAのコントローラーは、他のことを気にせずに、メモリからLCDにデータを単に「循環」させることができます。

ドライバーで最後に興味があるのは、プローブ機能です。

ドライバープローブ機能

struct fb_info *info; int ret; u32 vmem_size; unsigned char *vmem; dma_addr_t dma_addr; pdev->dev.dma_mask = &platform_dma_mask; pdev->dev.coherent_dma_mask = DMA_BIT_MASK(32); vmem_size = (etn_fb_var.width * etn_fb_var.height * etn_fb_var.bits_per_pixel) / 8; vmem = dmam_alloc_coherent(&pdev->dev, vmem_size, &dma_addr, GFP_KERNEL); if (!vmem) { dev_err(&pdev->dev, "FB: dma_alloc_coherent error\n"); return -ENOMEM; } memset(vmem, 0, vmem_size); info = framebuffer_alloc(0, &pdev->dev); if (!info) return -ENOMEM; info->screen_base = vmem; info->fbops = &etn_fb_ops; info->fix = etn_fb_fix; info->fix.smem_start = dma_addr; info->fix.smem_len = vmem_size; info->var = etn_fb_var; info->flags = FBINFO_DEFAULT; info->pseudo_palette = &etn_fb_pseudo_palette; /* Get FPGA registers address */ fpga_regs = devm_ioremap(&pdev->dev, FPGA_REGS_BASE, REGSIZE); /* Disable refreshing */ fpga_write_reg(LCD_DMA_CR, 0); lcd_init(info); set_dma_addr(dma_addr); set_fps(fps); /* Enable refreshing */ fpga_set_bit(LCD_DMA_CR, LCD_DMA_CR_REDRAW_EN); ret = register_framebuffer(info); if (ret < 0) { framebuffer_release(info); return ret; } platform_set_drvdata(pdev, info); return 0;

それで何が起こっていますか?

まず、 dmam_alloc_coherent()関数を使用して、DMA互換ゾーンにメモリを割り当てます。 この場合、選択した領域を「指す」2つのアドレスを取得します。 1つはドライバーで使用され、2つ目はFPGAに書き込み、DMAコントローラーがこの領域からデータを読み取れるようにします。

DMAマッピングについて簡単に説明します。 これらには2つのタイプがあります。

- ストリーミング

- 合意(一貫性または一貫性)

一貫したマッピングは、プロセッサとデバイスの両方で同時に利用できます。 アクセスすると、各当事者は「新鮮な」データを受け取ることが保証されます。 バッファーがドライバーの存続期間を通じて存在する場合に最もよく使用されます。 使用例は、フレームバッファメモリです。

ストリーミングマッピングを使用する場合、厳密に順番にアクセスできます。 ほとんどの場合、それらは1つの操作中に作成されます。

理論的には、より生産的かもしれません。 例は、ネットワークパケットの受信/送信です。

プローブ機能に戻ります。 次に、 fb_infoに入力します。

次に、ステータス制御レジスタを読み書きできるように、FPGAアドレス空間をマップします。

その後、必要なFPS値とDMAアドレスをFPGAに書き込みます(必要に応じて、ワード番号に変換することを忘れないでください)。

次に、FPGAでのレンダリングを有効にして、フレームバッファーを登録します。 すべて準備完了です!

FPGAのモジュール

FPGAのモジュールに到達しました。 ここでも、すべてが簡単です。

実装する必要があることを思い出させてください:

- CPUからLCDへの直接アクセス

- フレームバッファメモリの読み取り

- LCDへの書き込みトランザクションの形成

- 適切なFPSを取得する

当然、制御レジスタはCPUからLCDへの直接アクセスを提供するために使用されます。

そして、通常のマルチプレクサ-制御がCPUから来る場合、レジスタからの信号はLCDへのインターフェースに切り替えられ、そうでない場合は-モジュールからFPGAへの信号。 選択は、ステートマシンの状態によって異なります。これについては、以下で説明します。

コードはプリミティブです:

LCDバスMUX

always_ff @( posedge clk_i ) if( state == IDLE_S ) begin lcd_bus_if.data <= lcd_ctrl_if.data; lcd_bus_if.rd <= lcd_ctrl_if.rd; lcd_bus_if.wr <= lcd_ctrl_if.wr; lcd_bus_if.rs <= lcd_ctrl_if.rs; end else // Send data transactions from FPGA. begin lcd_bus_if.data <= lcd_data_from_fpga; lcd_bus_if.rd <= 1'b1; lcd_bus_if.wr <= lcd_wr_from_fpga; lcd_bus_if.rs <= 1'b1; end

次のタスクは、メモリからデータを読み取り、LCDに書き込むことです。 ここで少し考える必要があります。

読み取りインターフェイスのスループットは、LCDにデータを書き込む速度よりもはるかに大きいため、連続してデータを読み取ることはできません(ドキュメントに示されているタイムスタンプを確認する必要があることに注意してください)。

つまり、人為的に読み取り速度を制限する必要があります。 これには次のオプションがあります。

- LCDへの読み取りと書き込み-読み取り、書き込み、読み取り、書き込みなど

- データを読み取り、維持する必要がある速度を計算します

- FIFOを使用

最初のオプションは、LCD上のデータに大きな(FPGA規格による)一時停止が発生するという事実につながります。

適用された問題(50を超えるFPSを取得する必要はほとんどありません)を考慮すると、これで十分である可能性が十分にあります。

しかし、それは非常に不器用でugいです。 したがって、このオプションは破棄します。

2番目のオプションは、LCDに連続ストリームを取得できるように、メモリからデータを読み取るのに必要な速度を計算することです。 また、特に出力ストリームの速度の一定性に関する厳密な要件がないことを考慮すると、非常に有効なオプションです。 ただし、一般的なケースでは、読み取りトランザクションの遅延の変数値により、バッファを使用して速度を調整する必要があります。

3番目のオプションは非常にシンプルで、かなり信頼性があります。 その本質は、メモリから読み取ったデータを高速で書き込むFIFOを使用することです。 バッファーのスペースがなくなると、読み取りを一時停止します。 同時に、バッファからデータを連続して読み取り、一定の速度でLCDにトランザクションを形成できます。 FIFOに場所が表示されるとすぐに、再びメモリからの読み取りを再開します。

3番目のオプションを選択します。 最初にFIFOが必要です。

FIFOインスタンス

buf_fifo #( .AWIDTH ( FIFO_AWIDTH ), .DWIDTH ( AMM_DATA_W ) ) buf_fifo ( .clock ( clk_i ), .aclr ( ), .wrreq ( fifo_wr_req ), .data ( fifo_wr_data ), .rdreq ( fifo_rd_req ), .q ( fifo_rd_data ), .almost_full ( ), .full ( ), .empty ( fifo_empty ), .usedw ( fifo_usedw ) );

読み取りを一時停止するタイミングを判断するには、すでにいっぱいになっているFIFOの量を知るだけでは不十分です。 結局、読み取りトランザクションもあり、それらは現在処理中です。 つまり、読み取りが既に要求されているが、まだ配信されていないデータです。

そのようなトランザクションの数を現時点で知る必要があります。 これを行うには、読み取り要求が実行されるたびに、対応するカウンターを増やし、読み取りデータの確認を受け取ったら、それを減らします。

保留中のトランザクションの計算

// Count of read transactions in progress logic [FIFO_AWIDTH-1:0] pending_read_cnt; always_ff @( posedge clk_i ) case( { read_req_w, amm_if.read_data_val } ) 2'b01: pending_read_cnt <= pending_read_cnt - 1'd1; 2'b10: pending_read_cnt <= pending_read_cnt + 1'd1; endcase

その結果、「処理中」にFIFOに記録された単語とトランザクションの合計がラインナップの深さにほぼ等しくなったときに読み取りを停止します。 「ほぼ」50個の自由な単語を選択します。

読むのをやめる

logic stop_reading; assign stop_reading = ( pending_read_cnt + fifo_usedw ) > ( 2**FIFO_AWIDTH - 'd50 );

Avalon MMでの読み取りトランザクション自体の形成は原始的です。 主なことは、インターフェイスのタイプに応じてアドレスを正しくインクリメントすることです: fpga2sdramまたはfpga2hps (インターフェイスおよび違いの詳細については、 こちらを参照してください ):

読み取りトランザクション

// fpga2sdram used word address, so we must added 1 every time, // fpga2hps used byte address, so we must added 8 (for 64-bit iface). logic [31:0] addr_incr; assign addr_incr = ( USE_WORD_ADDRESS == 1 ) ? 1 : ( AMM_DATA_W >> 3 ); always_ff @( posedge clk_i ) if( state == IDLE_S ) amm_if.address <= lcd_ctrl_if.dma_addr; else if( read_req_w ) amm_if.address <= amm_if.address + addr_incr; // Always read all bytes in word assign amm_if.byte_enable = '1; // We don't use burst now assign amm_if.burst_count = 1; assign amm_if.read = ( state == READ_S ); // Remove Quartus warnings assign amm_if.write_data = '0; assign amm_if.write = 0;

データを読むことを学んだので、今度はLCDにデータを書き込む方法を学ぶ必要があります。 これを行うには、2つの状態の単純なステートマシンを作成します。FIFOにデータがある場合、マシンはトランザクション送信状態になります。 そして、記録が終了すると、IDLEに戻ります。

LCDに書き込むためのFSM

enum int unsigned { LCD_IDLE_S, LCD_WRITE_S } lcd_state, lcd_next_state; always_ff @( posedge clk_i ) lcd_state <= lcd_next_state; always_comb begin lcd_next_state = lcd_state; case( lcd_state ) LCD_IDLE_S: begin if( !fifo_empty ) lcd_next_state = LCD_WRITE_S; end LCD_WRITE_S: begin if( lcd_word_cnt == 5'd31 ) lcd_next_state = LCD_IDLE_S; end endcase end assign fifo_rd_req = ( lcd_state == LCD_IDLE_S ) && ( lcd_next_state == LCD_WRITE_S );

LCDが16ビットのデータを転送する前に1つのトランザクションを覚えておく必要があり、FIFOの各ワードのサイズは64ビットです(fpga2sdram / fpga2hpsインターフェイスの構成によって異なります)。 したがって、読む単語ごとに4つのトランザクションを形成します。

それらを簡単に作成できます。このため、1つのカウンターを作成し、その中の必要なビットを使用するだけで十分です。

読み取りトランザクション

// ILI9341 Data transaction from FPGA: // __ __ __ __ __ __ __ __ __ // clk/4 | __| |__| |__| |__| |__| |__| |__| |__| |__| | // // data | ///< split[0] | split[1] | split[2] | split[3] >//// // // _______________________________________________ // rd | xxxx xxxx // // _____ _____ _____ _____ // wr | xxxx_____| |_____| |_____| |_____| xxxx // // _______________________________________________ // rs | xxxx xxxx logic [3:0][15:0] fifo_rd_data_split; assign fifo_rd_data_split = fifo_rd_data; logic [15:0] lcd_data_from_fpga; logic lcd_wr_from_fpga; logic [4:0] lcd_word_cnt; always_ff @( posedge clk_i ) if( lcd_state == LCD_IDLE_S ) lcd_word_cnt <= '0; else lcd_word_cnt <= lcd_word_cnt + 1'd1; assign lcd_data_from_fpga = fifo_rd_data_split[ lcd_word_cnt[4:3] ]; assign lcd_wr_from_fpga = ( lcd_state == LCD_IDLE_S ) ? 1'b1 : lcd_word_cnt[2];

ほとんどすべて。 上記のすべてを管理するメインステートマシンを作成します。

その動作のロジックは単純です-LCDコントローラモジュールがオンになっている場合、1つのフレームを描画する必要があります。

特定のFPSを実装するために、目的のティック数が予想される「一時停止状態」があります。

その後、メモリからのデータの読み取りが開始されます(データがFIFOに表示されるとすぐにLCDへの書き込みが自動的に開始されます)。

フレーム全体が読み取られると、残っているのはLCDへのトランザクションの完了を待つことだけです。

メインFSM

logic [31:0] word_cnt; always_ff @( posedge clk_i ) if( state == IDLE_S ) word_cnt <= '0; else if( read_req_w ) word_cnt <= word_cnt + 1'd1; logic reading_is_finished; assign reading_is_finished = ( word_cnt == WORD_IN_FRAME - 1 ) && read_req_w; logic stop_reading; assign stop_reading = ( pending_read_cnt + fifo_usedw ) > ( 2**FIFO_AWIDTH - 'd50 ); logic all_is_finished; assign all_is_finished = ( pending_read_cnt == 0 ) && ( fifo_usedw == 0 ) && ( lcd_state == LCD_IDLE_S ); enum int unsigned { IDLE_S, FPS_DELAY_S, READ_S, WAIT_READIND_S, WAIT_WRITING_S } state, next_state; always_ff @( posedge clk_i ) state <= next_state; // FIXME: // If lcd_ctrl_if.redraw_en == 1 // CPU have one takt for read 0 in lcd_ctrl_if.dma_busy // Fix: add WAIT_WRITING_S -> FPS_DELAY_S path always_comb begin next_state = state; case( state ) IDLE_S: begin if( lcd_ctrl_if.redraw_stb || lcd_ctrl_if.redraw_en ) next_state = FPS_DELAY_S; end FPS_DELAY_S: begin if( fps_delay_done_w ) next_state = READ_S; end READ_S: begin if( reading_is_finished ) next_state = WAIT_WRITING_S; else if( stop_reading ) next_state = WAIT_READIND_S; end WAIT_READIND_S: begin if( !stop_reading ) next_state = READ_S; end WAIT_WRITING_S: begin if( all_is_finished ) next_state = IDLE_S; end endcase end

これで、LCDコントローラーの準備が整いました。

U-bootセットアップ

前の記事で 、 fpga2sdramインターフェースをオンにすることはU-bootで行う必要があると書きました。 そうしないと、読み取りトランザクション中に、システムが完全にフリーズします。 これを行うには、環境に次の行を追加します。

u-boot-env.txt

... fpgadata=0x10000000 fpgafile=/lib/firmware/fpga/fpga.rbf fpgaboot=setenv fpga2sdram_handoff 0x3fff; ext2load mmc 0:2 ${fpgadata} ${fpgafile}; fpga load 0 ${fpgadata} ${filesize} bridge_enable_handoff=mw $fpgaintf ${fpgaintf_handoff}; go $fpga2sdram_apply; mw $fpga2sdram ${fpga2sdram_handoff}; mw $axibridge ${axibridge_handoff}; mw $l3remap ${l3remap_handoff} bootcmd=run fpgaboot; run bridge_enable_handoff; run mmcboot ...

デバッグ

原則として、すべてが問題なく動作するはずなので、デバッグするものは何もありません。

しかし、私たちは少し面倒で、FPGAモジュールのテストベンチを作成しなかったので、安心のためにSignalTapでモジュールの動作を見る価値があります。

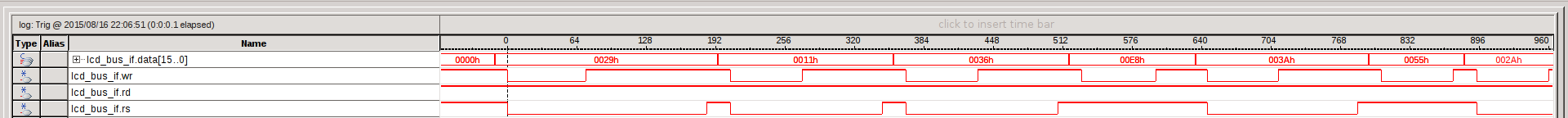

これは、CPUからのトランザクションの外観です。

コマンド0x29、0x11、0x36およびデータ0xE8の記録が表示されます。 そうです。

したがって、FPGAからのトランザクションは次のようになります。

そして、ここでも、すべてが計画どおりです。

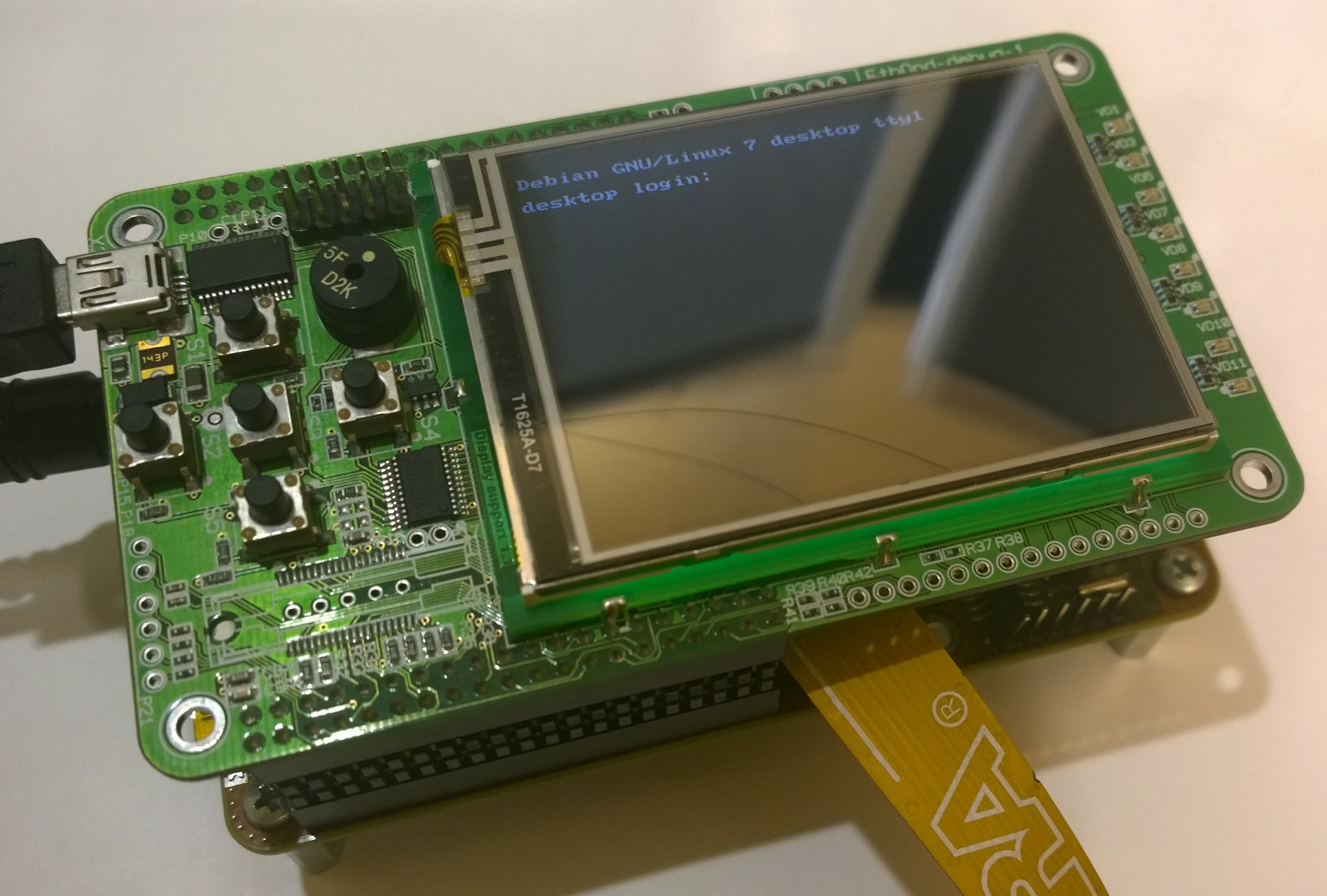

やった! FPGAにLCDコントローラーがあります。

最後まで読んでくれた人に感謝します! 頑張って

便利なリンク

githubのソース

すべての作業が実行されたデバイス

フレームバッファードライバーを記述するためのドキュメント

ILI9341ドキュメント

前の記事に関するメモ

前回の記事では、 fpga2sdramインターフェースの帯域幅を測定しました。

残念ながら、私は間違いを犯しました。 つまり、PLLシュレッドは実際の25 MHzではなく125 MHzに設定されました。

このため、PLLの乗数と除数の比率は正しく計算されませんでした。

その結果、DDR3は規定の333 MHzではなく66 MHzで動作しました。

正しい係数と256ビットのインターフェイス幅を使用すると、スループットは約16〜17 Gbit / sになります。これは、幅が32ビットで周波数が333 MHzのDDR3インターフェイスの理論上のスループットに相当します。

おaびします!

小規模な調査

コミュニティの意見を知りたいです。 難しくなければ、投票してください。