最近、AVRマイクロコントローラーの信号発生器のプロジェクトを見ました。 生成の原理はDDSで、 Jesperライブラリに基づいて、最大周波数は65534 Hz(および蛇行のある最大8 MHzのHS出力)です。 そして、FPGAが可能な限り最良の方法でそれ自体を表示できるジェネレーターは素晴らしいタスクだと思いました。 スポーツの関心事として、私はFPGAでプロジェクトを繰り返し、2日間の締め切りに間に合わせることにしました。パラメーターは厳密に定義されていませんでしたが、可能な限り最大でした。 これから来たものは、あなたがカットの下で見つけることができます

最近、AVRマイクロコントローラーの信号発生器のプロジェクトを見ました。 生成の原理はDDSで、 Jesperライブラリに基づいて、最大周波数は65534 Hz(および蛇行のある最大8 MHzのHS出力)です。 そして、FPGAが可能な限り最良の方法でそれ自体を表示できるジェネレーターは素晴らしいタスクだと思いました。 スポーツの関心事として、私はFPGAでプロジェクトを繰り返し、2日間の締め切りに間に合わせることにしました。パラメーターは厳密に定義されていませんでしたが、可能な限り最大でした。 これから来たものは、あなたがカットの下で見つけることができます ゼロ日

週末が来る前に、実装について少し考える時間がありました。 タスクを簡素化するため、ボタンとLCDスクリーンを備えた個別のデバイスとしてではなく、USB経由でPCに接続するデバイスとしてジェネレーターを作成することにしました。 このために、USB2RS232ボードがあります。 ドライバーボードは(CDC)を必要としないため、Linuxで動作すると思います(誰かにとって、これは重要です)。 また、RS232を介したメッセージの受信で既に作業したという事実を隠しません。 RS232を操作するためのモジュールは、 opencores.comから既製のものを取ります。

週末が来る前に、実装について少し考える時間がありました。 タスクを簡素化するため、ボタンとLCDスクリーンを備えた個別のデバイスとしてではなく、USB経由でPCに接続するデバイスとしてジェネレーターを作成することにしました。 このために、USB2RS232ボードがあります。 ドライバーボードは(CDC)を必要としないため、Linuxで動作すると思います(誰かにとって、これは重要です)。 また、RS232を介したメッセージの受信で既に作業したという事実を隠しません。 RS232を操作するためのモジュールは、 opencores.comから既製のものを取ります。 正弦波信号を生成するには、DACが必要です。 元のプロジェクトのように、DACのタイプを選択しました-8ビットのR2R 。 メガヘルツ程度の高周波数で作業できます。 FPGAはこれに対処しなければならないと確信しています

COMポートを介してデータを送信するためのプログラムを書くことについては、私は考えました。 一方では、Delphi7で記述できます。すでにそのようなプログラムを記述した経験があり、実行可能ファイルのサイズは大きくありません。 また、htmlページでSerialをJavaスクリプトとして動作させるために何かを書き留めようとしましたが、多かれ少なかれChromeシリアルAPIを介してのみ動作しましたが、このためにプラグインをインストールする必要があります...一般に、それも消えます。 私自身の革新として、PyQt5を試しましたが、そのようなプロジェクトを配布するときは、たくさんのライブラリをドラッグする必要があります。 PyQtプロジェクトをexeファイルで収集しようとすると、10 MB以上になりました。 つまり、c ++ \ Qt5で記述されたアプリケーションよりも優れているわけではありません。 Pythonの開発経験はありませんが、Qt5で開発経験があることを考慮する価値があります。 したがって、選択肢はQt5に落ちました。 5番目のバージョンでは、シリアルを操作するためのモジュールが登場しましたが、私はすでにそれを操作していました。 また、Qt5のアプリケーションはLinuxおよびMacに移植でき(一部の人々にとってこれは重要です)、バージョン5.2以降、QWidgetsのアプリケーションはスマートフォンに移植することさえできます!

COMポートを介してデータを送信するためのプログラムを書くことについては、私は考えました。 一方では、Delphi7で記述できます。すでにそのようなプログラムを記述した経験があり、実行可能ファイルのサイズは大きくありません。 また、htmlページでSerialをJavaスクリプトとして動作させるために何かを書き留めようとしましたが、多かれ少なかれChromeシリアルAPIを介してのみ動作しましたが、このためにプラグインをインストールする必要があります...一般に、それも消えます。 私自身の革新として、PyQt5を試しましたが、そのようなプロジェクトを配布するときは、たくさんのライブラリをドラッグする必要があります。 PyQtプロジェクトをexeファイルで収集しようとすると、10 MB以上になりました。 つまり、c ++ \ Qt5で記述されたアプリケーションよりも優れているわけではありません。 Pythonの開発経験はありませんが、Qt5で開発経験があることを考慮する価値があります。 したがって、選択肢はQt5に落ちました。 5番目のバージョンでは、シリアルを操作するためのモジュールが登場しましたが、私はすでにそれを操作していました。 また、Qt5のアプリケーションはLinuxおよびMacに移植でき(一部の人々にとってこれは重要です)、バージョン5.2以降、QWidgetsのアプリケーションはスマートフォンに移植することさえできます! 他に何が必要ですか? FPGAを搭載したマザーボード。 2つあります(10,000セルの場合はcyclone iv EP4CE10E22C8N、5,000セルの場合はCyclone ii EP2C5)。 より便利なコネクタのためだけに、左側のものを選択します。 ボリュームの面では、プロジェクトは大きくなることを意図していないため、2つのいずれにも適合します。 速度に違いはありません。 両方のボードには「オンボード」の50 MHzオシレータがあり、FPGA内にはPLLがあり、これを使用して周波数を200 MHzに上げることができます。

初日

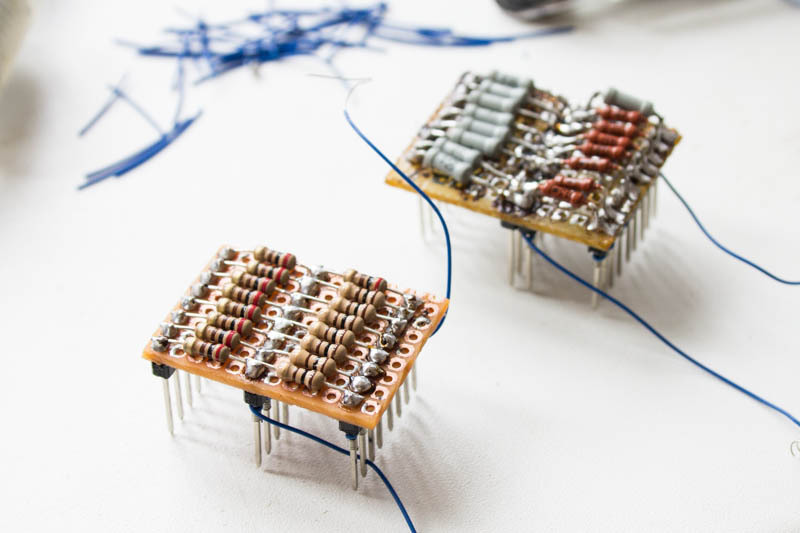

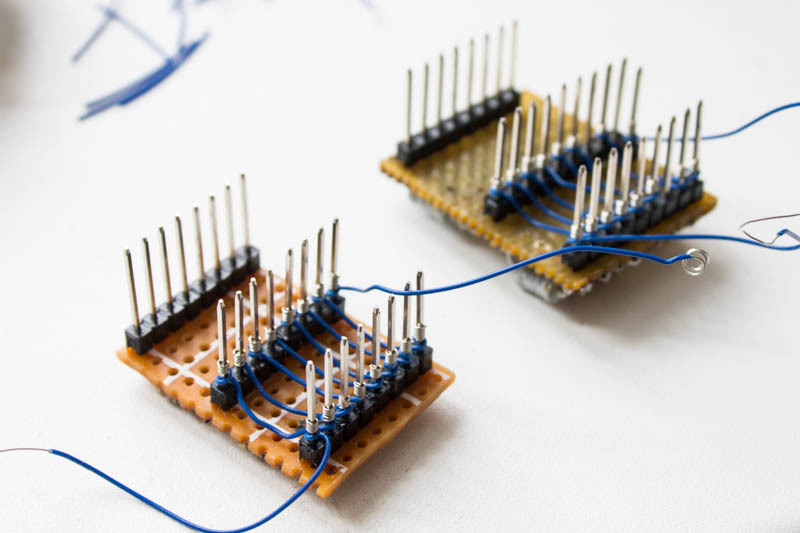

シンセサイザープロジェクトで既にDDSモジュールを使用したため、すぐにはんだごてを取り上げ、DACを抵抗にはんだ付けし始めました。 ブレッドボードを取りました。 インストールはラッピングを使用して行われました。 テクノロジーに影響を与えた唯一の変更点は、TTインジケーターフラックスゲルを支持して、 錫メッキラックの酸性F38Nを放棄したことです。 この技術の本質は簡単です。ラックをプリント基板にはんだ付けし、抵抗器をプリント回路側からはんだ付けします。 欠落している接続はラップされます。 それでも、ラックはFPGAボードに直接挿入できるという点で便利です。

残念ながら、自宅では抵抗器1および2キロオームはありませんでした。 店に行く時間はありませんでした。 ルールの1つを放棄し、古い不要なボードから抵抗を削除する必要がありました。 使用された抵抗器は15Kと30Kでした。 結果はそのようなフランケンシュタインです:

その後、Quartusを起動し、プロジェクトを作成しました

プロジェクトを作成したら、ターゲットデバイスを設定する必要があります。Assigmentsメニュー-> Device

次に、同じ場所で「デバイスとピンのオプション」ボタンをクリックします。ピンが機能しないように設定されているためです。 「通常のI / Oとして使用する」などのすべてを設定します

次に、同じ場所で「デバイスとピンのオプション」ボタンをクリックします。ピンが機能しないように設定されているためです。 「通常のI / Oとして使用する」などのすべてを設定します

このプロジェクトでは、アンマネージド固定周波数DDSメインモジュールを「びっくり」させました。

1000 Hzジェネレーターモジュール

module signal_generator(clk50M, signal_out); input wire clk50M; output wire [7:0] signal_out; wire clk200M; osc osc_200M reg [31:0] accumulator; assign signal_out = accumulator[31:31-7]; // 1000 //50 000 000 Hz - //2^32 = 4 294 967 296 - DDS - 32 // 1000Hz / 50 000 000 Hz / 2 * 4294967296 => 42949,67296 always @(posedge clk50M) begin accumulator <= accumulator + 32'd42949; end endmodule

その後、「Start Compilation」をクリックして、プロジェクトのメインモジュールに入力/出力ラインがあり、それらがどの物理PINに接続されているかを開発環境が疑問に思いました。 ほとんど誰にでも接続できます。 コンパイル後、表示された行をFPGAチップの実際のPINに割り当てます。

割り当て->ピンプランナーメニュー項目

HS_OUT、key0およびkey1行では、まだ注意を払わないでください。これらは後でプロジェクトに表示されますが、最初は画面を作成できませんでした。

原則として、Location列にPIN_nnのみを「登録」するだけで十分です。残りのパラメーター(I / O標準、現在のストレンチ、スルーレート)はデフォルトのままにするか、デフォルトで提供されるものと同じ(デフォルト)を選択して警告しないようにすることができますの。

原則として、Location列にPIN_nnのみを「登録」するだけで十分です。残りのパラメーター(I / O標準、現在のストレンチ、スルーレート)はデフォルトのままにするか、デフォルトで提供されるものと同じ(デフォルト)を選択して警告しないようにすることができますの。

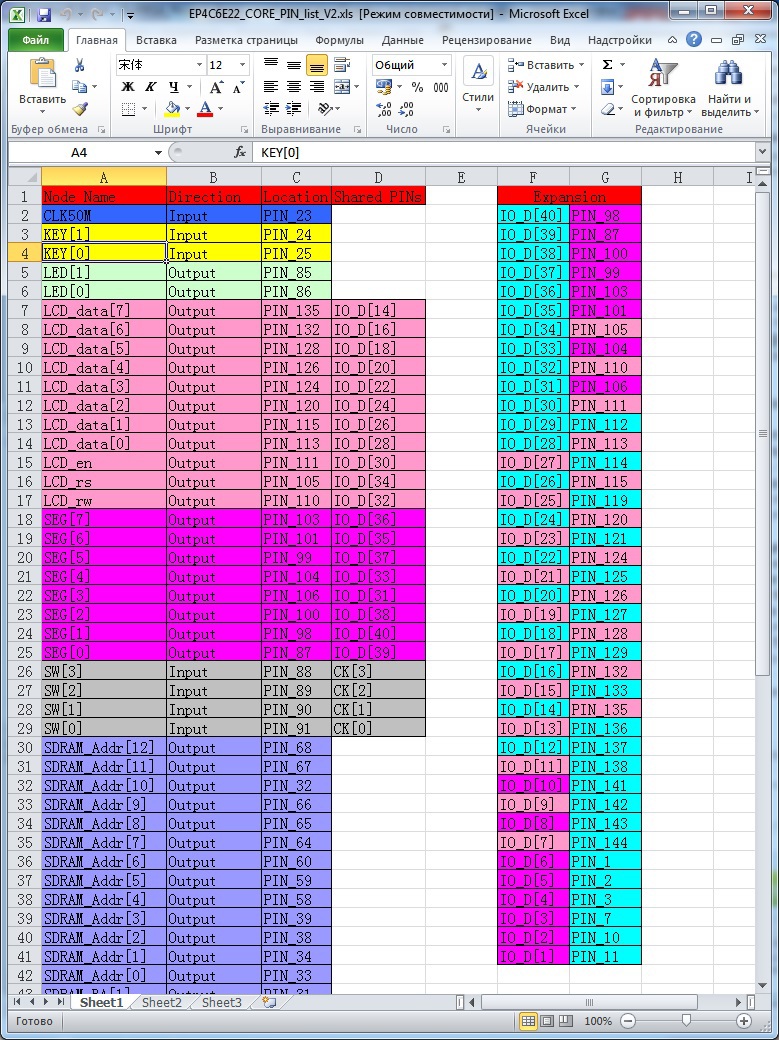

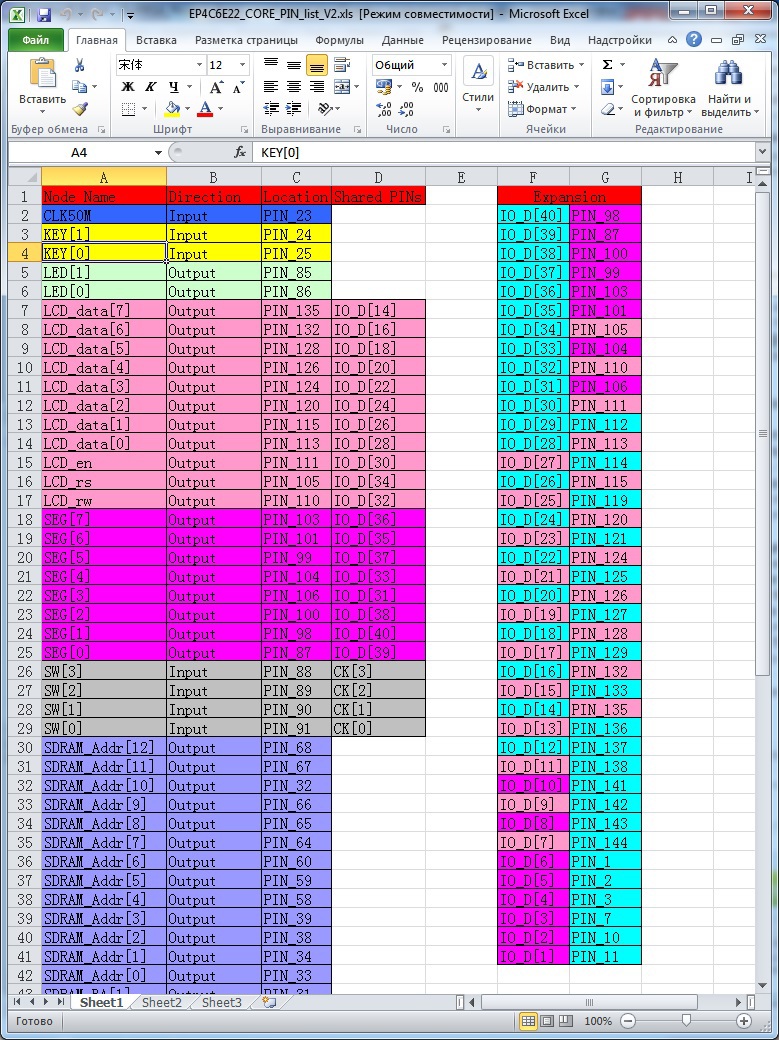

ボード上のスロット番号に対応するPINを見つける方法は?

コネクタのピン番号はボード上で署名されています

また、コネクタピンが接続されるFPGAピンについては、FPGAカードに付属のドキュメントに記載されています。

また、コネクタピンが接続されるFPGAピンについては、FPGAカードに付属のドキュメントに記載されています。

ピンを割り当てた後、プロジェクトを再度コンパイルし、USBプログラマーを使用してフラッシュします。 USB Byte blasterプログラマー用のドライバーをインストールしていない場合は、QuartusがインストールされているフォルダーにあることをWindowsに指定します。 その後、彼女は自分自身を見つけるでしょう。

プログラマーをJTAGコネクターに接続する必要があります。 プログラミングのメニュー項目は「ツール->プログラマ」です(またはツールバーのアイコンをクリックします)。 「スタート」ボタン、楽しい「成功」、ファームウェアはすでにFPGA内にあり、すでに動作しています。 FPGAをオフにしないでください。オフにすると、すべてを忘れてしまいます。

ツール->プログラマー

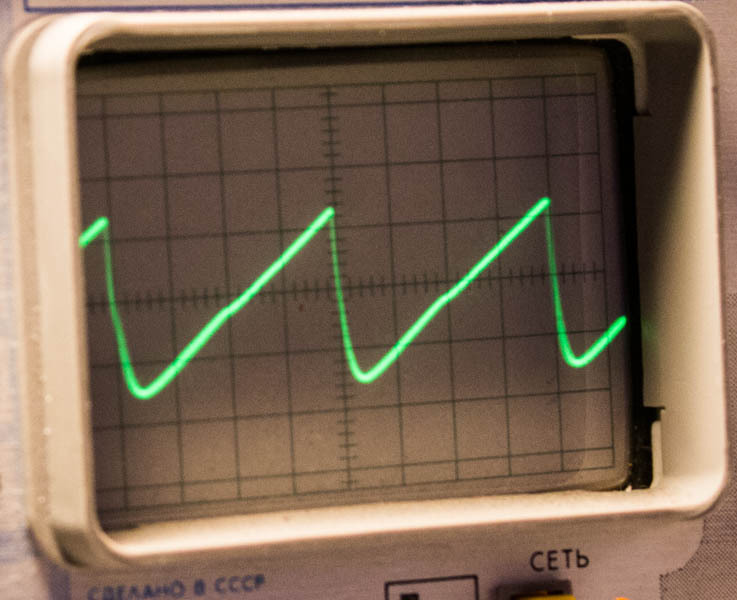

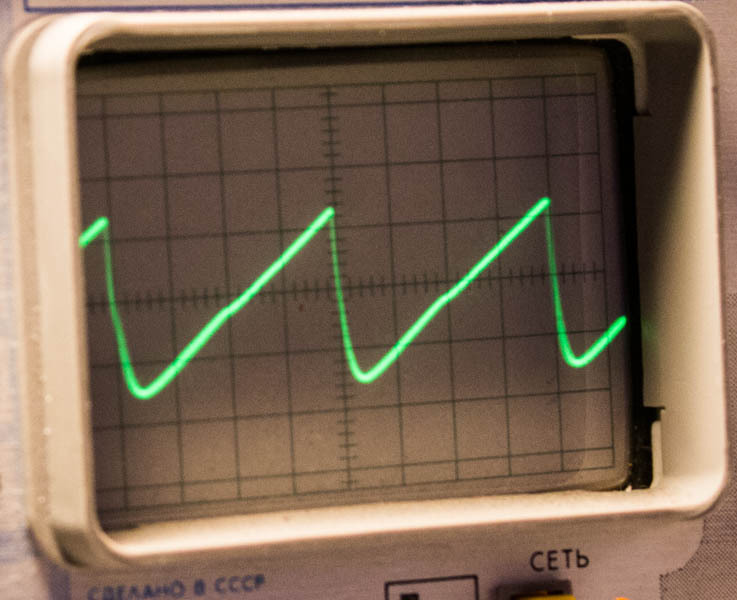

DACはFPGAボードコネクタに接続されます。 C1-112AオシロスコープをDAC出力に接続します。 位相アキュムレータのワードDDSの上位部分が8ビット出力に出力されるため、結果は「のこぎり」になるはずです。 そして、オーバーフローするまで常に増加します。

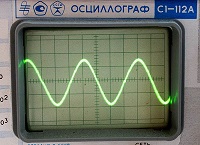

約1.5時間、周波数が1000 Hzの場合、次の波形が表示されます。

真ん中の「のこぎり」には小さな骨折があります。 これは、抵抗にはさまざまな値があるためです。

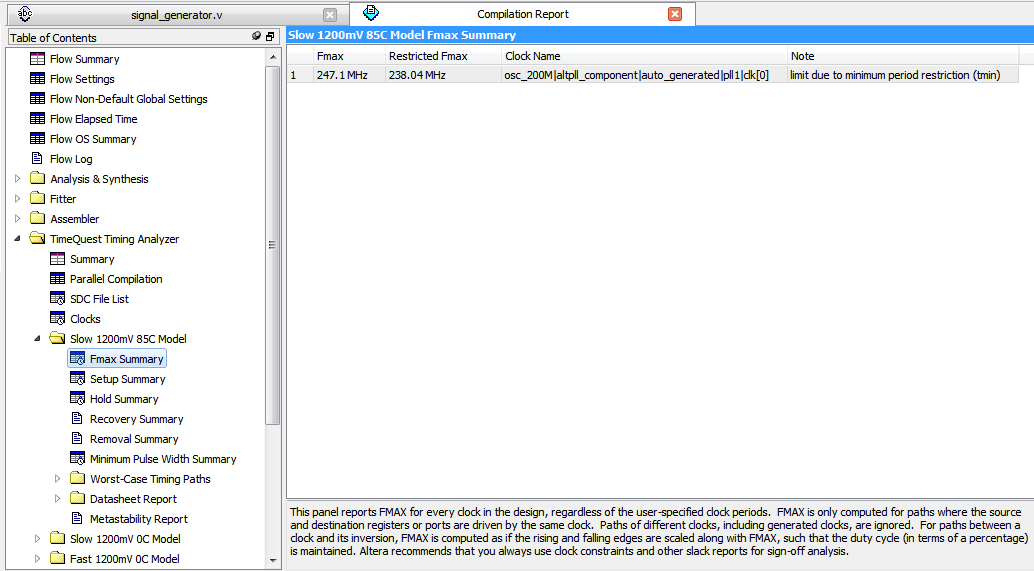

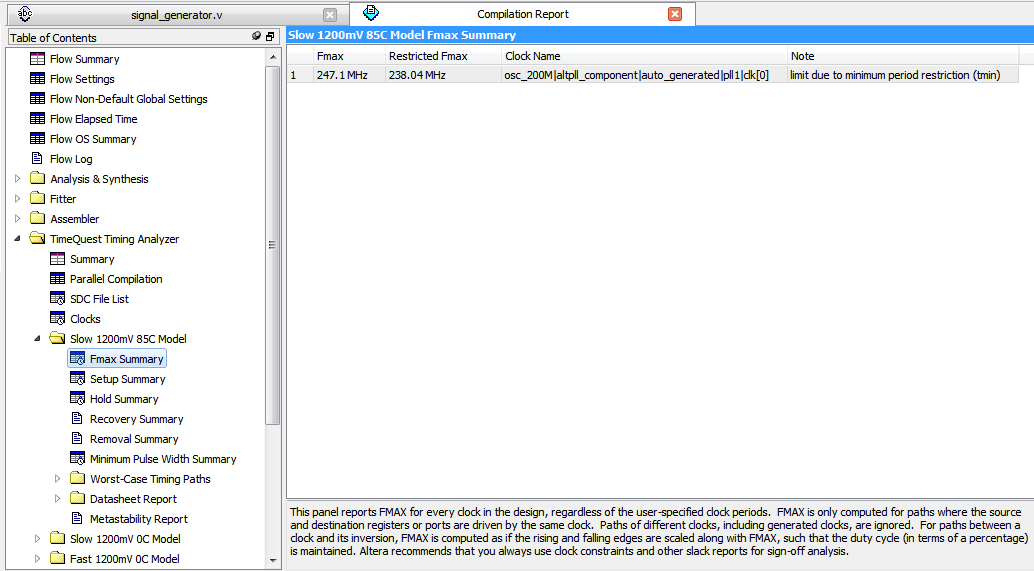

明確にする必要があるもう1つの重要な点は、DDSジェネレーターが動作する可能性のある最大周波数です。 TimeQuestパラメータを正しく構成すると、「Compilation Report」でコンパイルした後、回路の速度が余裕を持って200 MHzを超えていることがわかります。 これは、PLLを使用して50 MHz発振器の周波数に4を掛けることを意味します。200MHzの周波数でDDS位相バッテリーの値を増やします。 この条件で取得できる最終的な周波数範囲は0〜100 MHzです。 周波数設定精度:

200 000 000 (clk) / 2^32 (DDS) = 0,047

つまり、〜0.05 Hzよりも優れています。 このような動作周波数範囲(0〜100 MHz)の発電機のヘルツ分数の精度は十分であると考えています。 誰かが精度を上げる必要がある場合、これのDDS容量を増やすことができます(論理回路の速度が加算器であるため、CLK = 200 MHzであることをTimeQuest Timing Analyzerで確認することを忘れないでください)。広範囲の周波数は必要ありません。

TimeQuest Timing Analyzer

画面で「のこぎり」を見た後、家族のせいで私はその国(休日)に行くことを余儀なくされました。 そこでは、ケバブを刈り、調理し、グリルしました。そして、夕方に待っていたという驚きを疑いませんでした。 すでに夜に近づいて、寝る前に、他の周波数の波形を見ることにしました。

周波数が100 kHzの場合

250 kHzの周波数の場合

500 kHzの周波数の場合

周波数1 MHzの場合

特に1 MHz(悲惨で価値のないメガヘルツ!)で、波形が私をひっくり返すことを隠しません。 他のいくつかの注文の頻度を取得する予定でした。 R2R DACについて読んだ後、問題の原因が明らかになりました-浮遊容量。 したがって、翌日の計画では、私が持っている100および200オームの抵抗器でDACを作成し、そのような高周波での作業を必要としない将来の開発のためにこのDACを残すことが決定されました。鋸の滑らかさにも独自のプラスがあるためです。

二日目

DACが100オームの抵抗器と200オームの抵抗器でどのように機能するかがおもしろかったため、すぐにはんだごてを取り上げました。 今回はDACがより正確であることが判明し、インストールにかかる時間が短縮されました。

DACをFPGAボードに配置し、オシロスコープに接続します

1 MHz-INをチェックします! 完全に異なる問題!

10 MHzを見た

25 MHzを見た

10 MHzののこぎりの形状は、正しい形状と同様です。 しかし、25 MHzでは既に完全に「美しくありません」。 ただし、C1-112aの帯域幅は10 MHzであるため、この場合、理由はすでにオシロスコープにある可能性があります。

原則として、DACのこの問題はクローズドと見なすことができます。 それでは、高速出力波形を見てみましょう。 これを行うには、最上位ビットを別のPIN FPGAに出力します。 このラインのデータは、DDSバッテリーの最上位ビットから取得します。

assign hs_out = accumulator[31];

1 MHzの蛇行

5 MHzの蛇行

25 MHzの蛇行

50 MHzの蛇行はほとんど見えません

しかし、FPGA出力は抵抗に負荷をかける必要があると思います。 おそらく、前線はより急勾配になるでしょう。

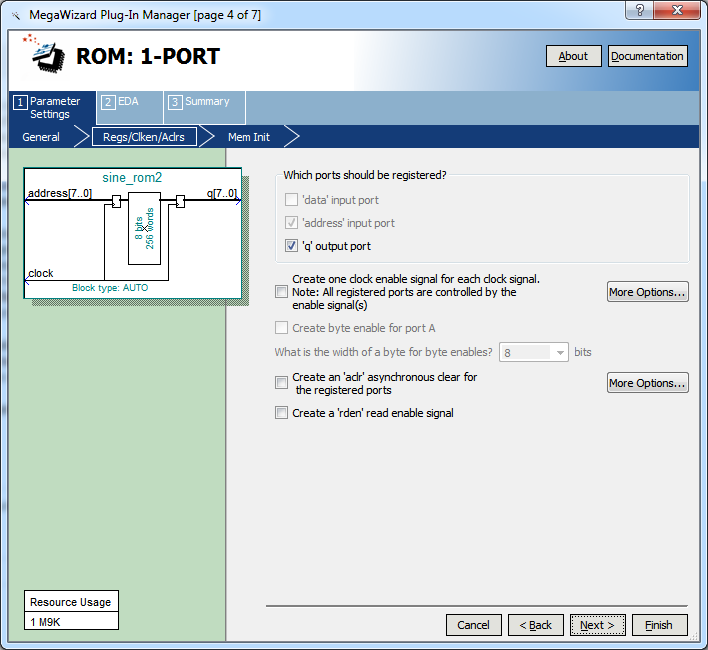

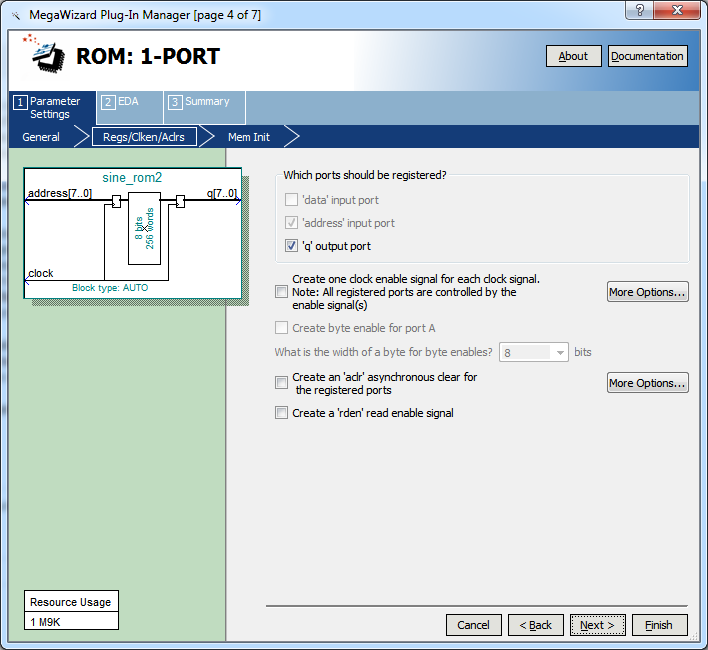

サインは表に従って行われます。 テーブルのサイズは8ビットの256値です。 1つ以上を使用できますが、すでに準備ができているmifファイルがあります。 ウィザードを使用して、mifファイルからのサインテーブルデータを使用してROM要素を作成します。

ROMの作成-ツール-> Mega Wizard Plugin manager

1つのポートROMを選択し、モジュールに名前を付けます

同意する

ここでも同意します

参照を使用して、sineテーブルを持つmifファイルを見つけます

ここでも何も変更しません

sine_rom_bb.vモジュールのチェックを外します-必要ありません。 次の仕上げ。 Quartusはモジュールをプロジェクトに追加するように要求します-同意します。 その後、モジュールはVerilogの他のモジュールと同じように使用できます。

1つのポートROMを選択し、モジュールに名前を付けます

同意する

ここでも同意します

参照を使用して、sineテーブルを持つmifファイルを見つけます

ここでも何も変更しません

sine_rom_bb.vモジュールのチェックを外します-必要ありません。 次の仕上げ。 Quartusはモジュールをプロジェクトに追加するように要求します-同意します。 その後、モジュールはVerilogの他のモジュールと同じように使用できます。

DDSバッテリワードの上位8ビットはROMアドレスとして使用され、データ出力はサイン値です。

コード

//sine rom wire [7:0] sine_out; sine_rom sine1(.clock(clk200M), .address(accumulator[31:31-7]), .q(sine_out));

異なる周波数での正弦波の波形は同じように見えます。

必要に応じて、抵抗の広がりに関連するDACの問題を検討できます。

さて、この週末は終わりました。 しかし、PCから管理するためのソフトウェアはまだ作成されていません。 締め切りに間に合わなかったという事実を認めなければなりません。

3日目

時間がほとんどないので、プログラムを急いで(最高の伝統で)書きます。 場所では、文字数を減らし、キーボードから情報を入力する便利さを減らすために、ウィジェットの名前によるイベントフィルターが適用されます。 ご理解とご容赦ください。

インターフェース

GitHubソースコード。 Windows用に構築されたアプリケーションが既にあります。

コードは5セントと同じくらい簡単です。 とりわけ、シリアルポートモジュールを.proプロジェクトファイルに追加する必要があります。

QT += core gui serialport

COMポートを開く

QSerialPort serial; ... serial.setPortName(ui->lbSerialPortInfo->currentText()); serial.setBaudRate(QSerialPort::Baud115200); serial.setDataBits(QSerialPort::Data8); serial.setParity(QSerialPort::NoParity); serial.setStopBits(QSerialPort::OneStop); serial.setFlowControl(QSerialPort::NoFlowControl); serial.open(QIODevice::ReadWrite);

メッセージの作成と送信

QByteArray source; QDataStream stream(&source, QIODevice::ReadWrite); stream << (qint8)(01); // set freq msg stream << waveform; stream << adder32; serial.write(source);

4日目

急いで、UARTデータの受信を完了しています。 UARTを介してメッセージを受信するには、いくつかのモジュールを配置する必要があります。 1つのボージェネレータ、2番目-レシーバ。 受信機が115200で動作するためには、メインクロック周波数が200 MHzであるという事実に基づいて計算を行う必要があります。

baud_genモジュール

parameter global_clock_freq = 200000000; parameter baud_rate = 115200; // - UART // first register: // baud_freq = 16*baud_rate / gcd(global_clock_freq, 16*baud_rate) //Greatest Common Divisor - . http://www.alcula.com/calculators/math/gcd/ // second register: // baud_limit = (global_clock_freq / gcd(global_clock_freq, 16*baud_rate)) - baud_freq // parameter GCD = (baud_rate==115200) ? 12800 : 0; parameter baud_freq = 16*baud_rate / GCD; parameter baud_limit = (global_clock_freq / GCD) - baud_freq; wire uart_clk; baud_gen BG(.clock(clk), .reset(rst), .ce_16(uart_clk), .baud_freq(baud_freq), .baud_limit(baud_limit));

メッセージを受信するためのモジュールを配置し、uart_clkとFPGAの物理入力からの信号が供給されます。

Uart_rxモジュール

//RCV wire [7:0] uart_command; wire uart_data_ready; uart_rx URX(.clock(clk), .reset(rst), .ce_16(uart_clk), .ser_in(rx), .rx_data(uart_command), .new_rx_data(uart_data_ready) );

次に、これらすべてを個別のモジュールに配置します。このモジュールは、波形の数と増分の値のみをDDSフェーズのバッテリーレジスタに出力します。

Ctrl.vモジュール

module ctrl(clk, rst, rx, wf, adder); input wire clk, rst, rx; output wire [7:0] wf; //wave form output wire [31:0] adder;// adder value reg [7:0] wf_reg; initial wf_reg <= 8'd0; reg [31:0] adder_reg; initial adder_reg <= 32'd1073741;

uart_rxモジュールは1バイトの情報を受信すると、1クロックサイクルの間、uart_data_ready行をユニットに入れます。 この時点で、受信したバイトはuart_command行にあります。 メッセージを受信するために、ステートマシンを作成しています。

ステートマシン

//rcv state machine parameter SM_READY = 4'd0; parameter SM_FRQ_WF = 4'd1; parameter SM_FRQ_DDS1 = 4'd2; parameter SM_FRQ_DDS2 = 4'd3; parameter SM_FRQ_DDS3 = 4'd4; parameter SM_FRQ_DDS4 = 4'd5; //messages parameter CMD_SETFREQ = 8'd1; reg [3:0] rcv_state; initial rcv_state <= SM_READY; always @ (posedge clk) begin if (uart_data_ready==1) begin if (rcv_state==SM_READY) begin rcv_state = (uart_command==CMD_SETFREQ) ? SM_FRQ_WF : rcv_state; end else if (rcv_state==SM_FRQ_WF) begin wf_reg <= uart_command; rcv_state <= rcv_state + 1'b1; end else if (rcv_state==SM_FRQ_DDS1) begin adder_reg <= (adder_reg << 8) + uart_command; rcv_state <= rcv_state + 1'b1; end else if (rcv_state==SM_FRQ_DDS2) begin adder_reg <= (adder_reg << 8) + uart_command; rcv_state <= rcv_state + 1'b1; end else if (rcv_state==SM_FRQ_DDS3) begin adder_reg <= (adder_reg << 8) + uart_command; rcv_state <= rcv_state + 1'b1; end else if (rcv_state==SM_FRQ_DDS4) begin adder_reg <= (adder_reg << 8) + uart_command; rcv_state <= SM_READY; end else begin rcv_state <= SM_READY; end end //ucom_ready end

モジュール出力にデータを出力します

おわりに

assign adder = adder_reg; assign wf = wf_reg;

メインモジュールに受信モジュールを追加します。

メインモジュールにctrlモジュールを追加します

//rs232 rcvr wire [31:0] adder_value; wire [7:0] waveform; ctrl ctrl_0(.clk(clk200M), .rst(rst), .rx(RS232in), .wf(waveform), .adder(adder_value));

増分値はアキュムレータフェーズに追加されます

サイクルごとにバッテリーの価値を高める

always @(posedge clk200M) begin accumulator <= accumulator + adder_value; end

位相アキュムレータ値の古い部分から、残りの波形を取得します。 そして、選択したフォームに応じて-出力に接続します。

波形

// wave_forms parameter SINE = 8'd0; parameter SAW = 8'd1; parameter RAMP = 8'd2; parameter TRIA = 8'd3; parameter SQUARE = 8'd4; parameter SAWTRI = 8'd5; parameter NOISE = 8'd6; wire [7:0] saw_out = accumulator[31:31-7]; wire [7:0] noise_out = 8'd127; //! wire [7:0] ramp_out = -saw_out; wire [7:0] square_out = (saw_out > 127) ? 8'b11111111 : 1'b00000000; wire [7:0] saw_tri_out = (saw_out > 7'd127) ? -saw_out : 8'd127 + saw_out; wire [7:0] tri_out = (saw_out>8'd191) ? 7'd127 + ((saw_out << 1) - 9'd511) : (saw_out>8'd063) ? 8'd255 - ((saw_out << 1) - 7'd127) : 7'd127 + (saw_out << 1); //sine rom wire [7:0] sine_out; sine_rom sine1(.clock(clk200M), .address(saw_out), .q(sine_out)); wire [7:0] signal = (waveform == SINE) ? sine_out : (waveform == SAW) ? saw_out : (waveform == RAMP) ? ramp_out : (waveform == TRIA) ? tri_out : (waveform == SQUARE) ? square_out : (waveform == SAWTRI) ? saw_tri_out : (waveform == NOISE) ? noise_out : 8'd127; //TODO

それがすぐに機能したことはほとんど驚きませんでした。 私が見つけた唯一のエラーは計算にありました:目的の周波数をCLKで除算し、さらに2つで除算してから、バッテリー容量を乗算しました。 ただし、バッテリーの値が0からMAXに変化するときに1期間を取得するため、これは必要ありません。 周波数アキュムレータの高次ビットを蛇行出力として使用する場合にのみ、さらに2で除算します(この場合、周波数は2倍低くなります)。 しかし、私は蛇行の領収書をやり直しました。

4日目

毎日記事を書くのに費やした時間を含めることができます。

検証に進みます。 まずはオシロスコープ。

28〜100 MHzの無線周波数では、ボードの隣にアンテナを配置して、SDRレシーバーを使用してジェネレーターを聴くことにしました。

結論

ITでよくあることですが、タイミングでエラーが2〜2.5回発生しました。 目標は達成されています:最大100 MHzのジェネレーターが膝に取り付けられています。 ただし、このクラフトを本格的なジェネレーターと呼ぶには、さらに作業する必要があります。 したがって、開発の大きな見通しがあります。 締め切りに失敗したため、原則としてできることは追加しませんでした。1)ノイズジェネレータ。 2)ユーザーが自分で描くウェーブジェネレーター。 3)デジタルシーケンスジェネレーター。 ジェネレーターにはまだ振幅とバイアスの調整はありません。

10000個中227個のセルを使用しました。他にプロジェクトに追加できるもののリスト:

- DACを展開する

- 生成された信号で出力数を増やす

- 大容量のDACチップを適用する

- 振幅およびオフセット制御を実装する

- 移植性のために、コントロール、LCDスクリーンを追加

- ノイズジェネレーターおよびその他の単純な波形を追加する

- 任意波形をロードする機能を追加します

誰でも自分でそれを行うことができ、必要な機能を備えたプロジェクトを拡張できると思います。 追加は最初から行うよりも簡単です。 制御コマンドの形式は非常に単純なので、ジェネレーターはマイクロコントローラーから制御できます。

ソースコード: https : //github.com/UA3MQJ/fpga-signal-generator

アナログとのリンク

完全なリストからはほど遠い

機能的なDDSジェネレーター。 AVRベースによって作成されました。 周波数0 ... 65534 Hz。

DDSジェネレーターGK101の概要。 アルテラのMAX240 FPGAで作成。 最大10 MHzの周波数。

PIC16F870のマルチファンクションジェネレーター。 周波数範囲:11 Hz-60 kHz。

アナログ関数発生器。 周波数範囲は20 Hz〜300 kHzです

AD9833のUSBファンクションジェネレーター。 DDSチップに基づいています。

Mini DDSは、最もシンプルな137 kHzトランスミッタなどです。 周波数136 kHz。

DDSは、PLMで「ジャンパー」制御を備えた機能ジェネレータです。