これらすべての年月にわたって、生産における多くの改善が導入され、超小型回路の構造は幅/長さだけでなく高さでも成長し始めました。 現在、CPUの構造は「メトロポリス」に似ています。 しかし、これらすべての年の間、主要なコンポーネントは変化していません-55年前のようなシリコンであり、今日ではチップの主要な部分です。 残念ながら、幸いなことに、これは永遠に続くことはできません。シリコンには限界があり、パフォーマンスを損なうことなくプロセスを10 nm以下に減らすことはできません、とIntelのエンジニアは言いました。

これらすべてにもかかわらず、同社は将来の計画を発表しました-それらを達成するために。 2018年までのマイクロチップの7 nmプロセス。 声明は良いですが、あなたは何でも言うことができます、それは計画を果たすために別の問題です。 Broadwellのリリースが数回延期されたという事実を考えると、3年後にしかわかりません。もっと長く待たなければならないかもしれません。 しかし、一つ良いことがあります。彼らには計画があります。

この計画は簡単です-シリコンの代わりに別の半導体を使用してください。 シリコンの後継機は、より大きな機動性を持つべきです。 移動度は、キャリアのドリフトと外部電界の間の比例係数です。 キャリアドリフトとは、外部電界の影響下で移動する電子の意図的な平均速度を意味します。 この領域ではモビリティが非常に重要です。なぜなら、その値が高いほど、より高密度で高速な回路を作成し、エネルギー消費を削減できるからです。

2016年には、CPUなどの10 nm製造プロセスの開発が約束されています。 このプロセスは、古典的な材料を使用して非常に実現可能です。 しかし、2018年はさらに興味深いものになると約束されています。同じIntelの代表者によると、従来のアプローチを使用した7 nmチップの生産はもはや不可能だからです。

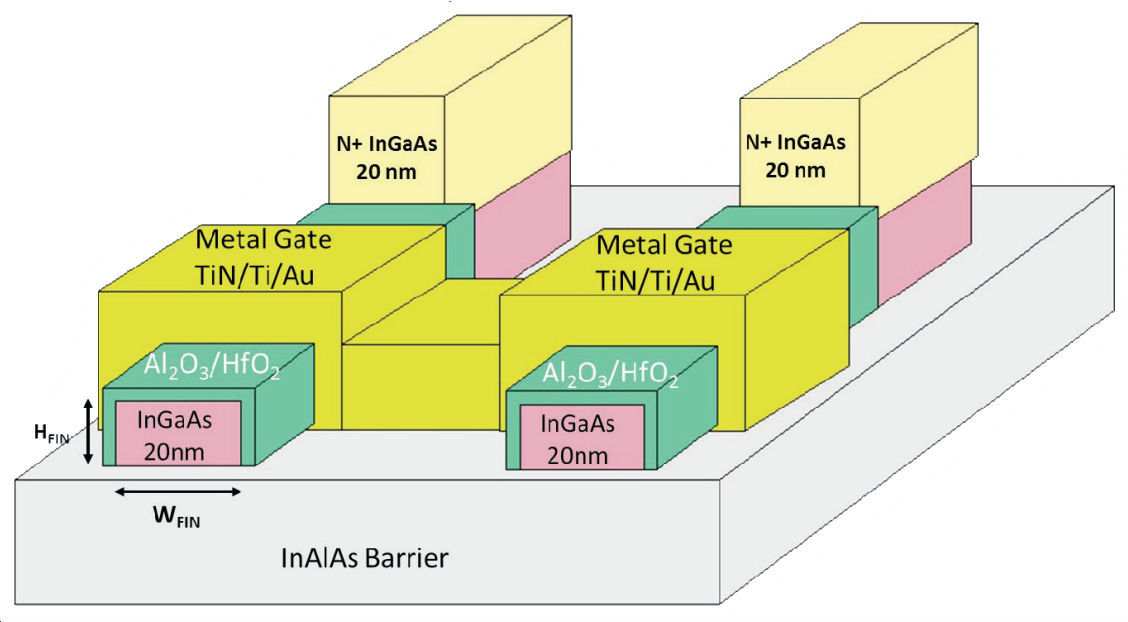

周期表からのさまざまな要素のソートは、実を結びました。 通常のシリコンに代わる代替材料の役割について、さまざまな候補が提案されています。 マイクロプロセッサの基本セルは、単一のトランジスタではなく、最小限の相補型(相補型)MOSトランジスタのペア-短いCMOSです。 このようなトランジスタは、nチャネルとpチャネルです。 nチャネルトランジスタには、インジウムガリウムヒ素からのInGaAs化合物が計画されています。 pチャネルトランジスタの場合、候補はシリコンに化学結合されたIV族ゲルマニウムでした。 ただし、この選択は最終的なものではありません。 上記の材料は、シリコンよりも高い移動度を持っています。

IntelのDavid Houseの意見:「プロセッサのパフォーマンスは18か月ごとに2倍になります」が、Intelのスローガンになりました。そのような結果は、ムーアの法則が守られた場合にのみ可能です:「集積回路のトランジスタ数は24か月ごとに2倍になりますしかし、法律がさらに数世代にわたって拡張されるようになったのは、トランジスタとその製造技術の進化だけです。そのため、企業はシリコントランジスタから離れなければなりません。

近年、インテルはこの法律を順守することが難しいと判断しました。 これの確認は、すでに述べたように、14 nm Broadwell技術プロセスを備えたマイクロチップのリリースが数回延期されたという事実です。 Broadwellの開発とリリースがIntelのマイクロチップの第2世代であるため、なぜこれが開発とリリースが遅れたのかは一見してわかりません。 Tri-Gateテクノロジーを搭載した最初の実験用トランジスタは2006年に導入されました。 Tri-Gateテクノロジーを搭載した最初の世代の22 nmマイクロチップは、2011年末に量産されたIvy Bridgeでした。

明らかに、問題の1つは、フォトリソグラフィーのプロセスにおけるマスクの数の増加でした。 これは、サブ波の深さが14 nmの画像に193 nmの紫外線を使用する問題に関連していると考えられます。 サブ波長リソグラフィーの開発と改善の長年にわたって、光学近接効果、マスクの相転移、高屈折率の液体への浸漬、繰り返し露光などのさまざまな側面を改善する多くの回避策が発見され、マスクの数が増加しました。

波長が13 nmに近い極端な紫外線リソグラフィーのアイデアと開発は2000年より前に生まれましたが、2000年代前半に100 nmのマイクロ回路が出現してすぐに縮小され再開されました。 現時点では、この技術の開発の成功は、7 nm製造プロセスの時代が始まるまで予想されていません。 主な問題の1つは、ビームのエネルギー源を見つけることです。 より短い波長の放射は、すべての物質に強く吸収されます。 真空中に置かれたミラー光学系の使用については、層間干渉に基づいた反射でしか考えられません。 マスク(フォトマスク)も反射要素の形で作られており、半透明ではありません。 各反射で、光線エネルギーの約1/3がミラーとマスクによって吸収されます。 7つのミラーを使用すると、ビーム出力の約94%が吸収されます。つまり、極端紫外線リソグラフィー(ESL)には強力な光源が必要です。 しかし、異なるマスクを使用したESMのインフラストラクチャにも問題があります。

同社は、14 nmの製造プロセスでマイクロチップを製造するコストを削減することはできませんでしたが、管理者は、現在の形の技術は単純化するよりも有用であると考えています。 10 nmの製造プロセスを備えた実験装置は、上位のBroadwellよりも50%高速であることが約束されており、その生産の遅れは予想されていません。これは重要です。

InGaAsまたはIII-IV族の他の元素の使用と量産への導入は、多くの困難を引き起こします。 私たちが直面しなければならない最初の問題は、直径30 cmの基板上にInGaAsを作成する技術の生産です。このような基板の製造は、マイクロチップの大量生産にとって非常に重要であり、これは単純な結論につながります-現在、シリコンの使用を完全に避けることは不可能です。

2013年、ルーベン(ベルギー)にあるImecナノエレクトロニクスセンターは、7 nm技術に適合したシリコン基板の生産技術を作成するための実験を開始しました。 シリコンウェーハがその後InGaAsウェーハに置き換えられる製造プロセス。 欧州研究センターは、シリコンウェーハをゲルマニウム製のウェーハに置き換えるための同様のプロセスも開発しました。 他の研究者は別のアプローチを開発しています-直径10 cmのリン化インジウム(InP)のわずかに小さいベース上にInGaAsのプレートを構築し、直接接続により30 cmシリコン基板にさらに移動します。 ただし、これはプロセスを複雑にし、それに応じて最終製品のコストが増加します。 そのようなポリシーは、単純な素人にとってチップを不採算にします。

また、InGaAsトランジスタのさらなる生産では、ソース/流出コンタクトなどの瞬間を考慮する価値があります。 多くの実験装置は7 nmプロセス技術には大きすぎ、シリコン媒体と適合しない材料を使用しています。

振動と伝導性の向上

アメリカと韓国の研究者は、サブスレッショルド発振の記録的な組み合わせを発表しました-82 mV /ディケード、0.5 V流出変位、導電率-1800μS/μm、InGaAs CMOSトランジスタの電流-0.41 mA /μm。 エピタキシャル構造は、分子線エピタキシーによりリン化インジウムの半絶縁性化合物上で成長しました。 エピタキシーとは、ある結晶性物質が別の結晶性物質の上に制御されて堆積することです。 分子線エピタキシーの場合、元素は非常に高い温度(400-800°C)で蒸発し、10 -6-10 -8 Paの圧力で過真空を使用すると、より低い温度で表面に元素の分子が沈殿します。

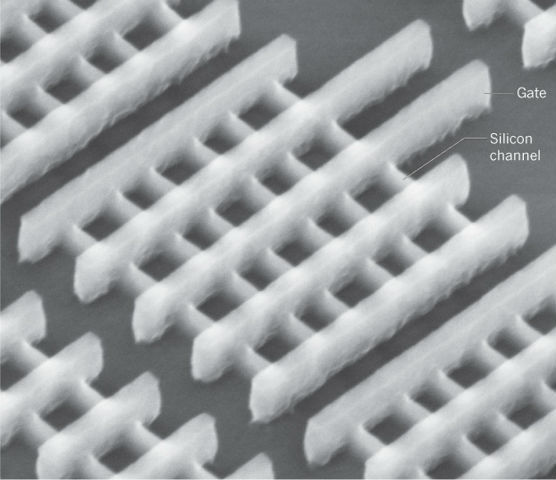

ウェット/ドライエッチングを組み合わせて、多層チップを使用してトラックの側面間の間隔を制御しました。 アレイの作成は、シャッターリブの希望の高さと幅を達成するために、電子ビームリソグラフィの2つのプロセスで構成されていました。 リブの最終的な高さと幅は、それぞれ20 nmと30 nmでした。

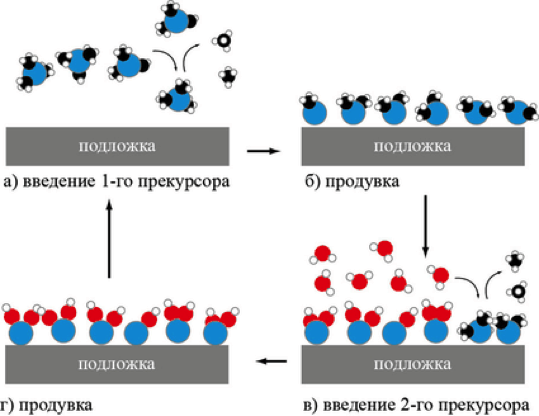

長さ80 nmのゲートを二酸化ケイ素(SiO 2 )の層に設置しました。 絶縁は、原子層堆積(ACO)の原理に従って、0.7 nmのアルミナ(Al 2 O 3 )と2 nmの二酸化ハフニウム(HfO 2 )で構成されていました。

酸化イットリウムの分離

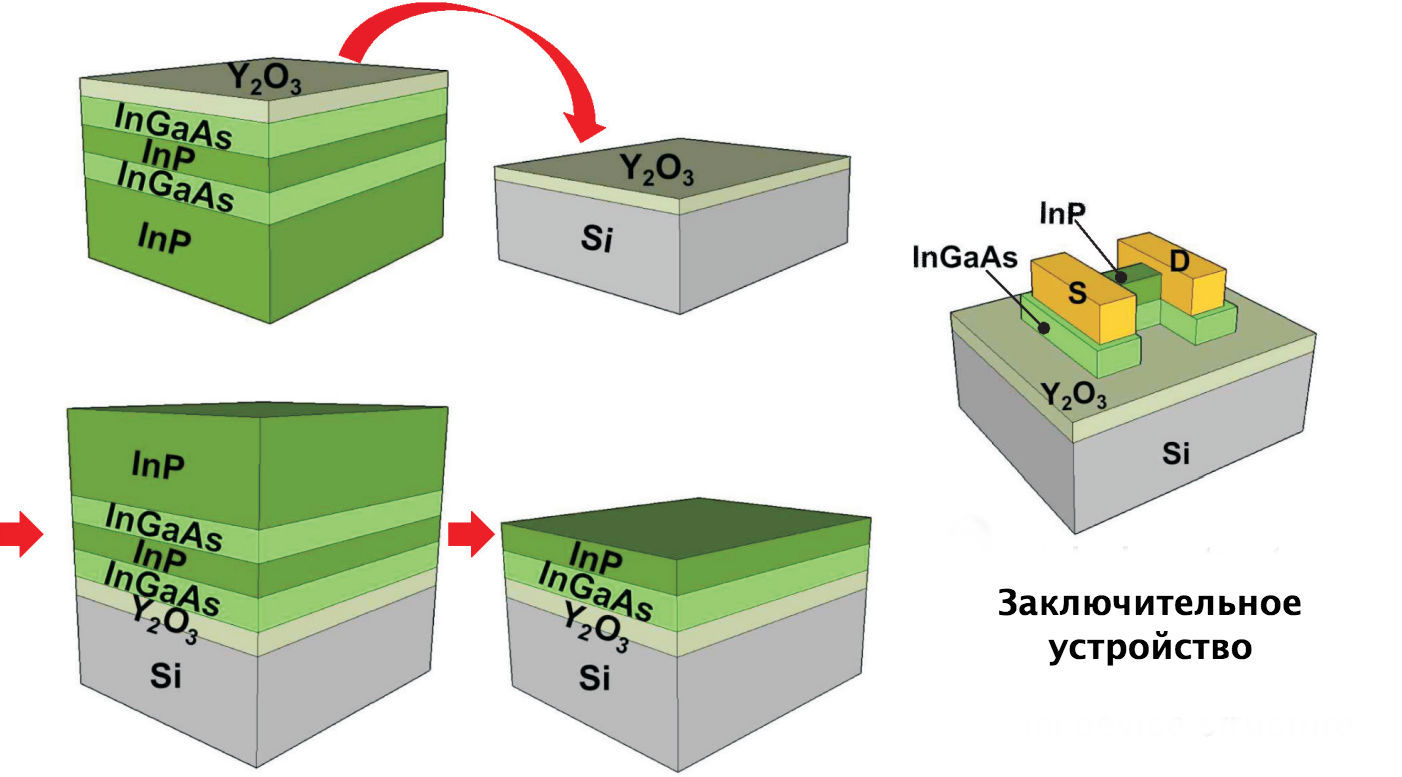

2015年3月31日、韓国科学技術院は、酸化イットリウム層に浸漬したInGaAsトランジスタを実証しました。 研究者は、InGaAsをより洗練されたTri-Gateテクノロジーの有望な代替手段と考えています。 Y 2 O 3を使用すると、誘電率が高い(16対9-12)アルミナに比べて、等価酸化膜厚(EOT)を減らすことができます。 興味深い事実は、水の誘電率が80であることです。 EOTを小さくすると、シャッターをチャネルの近くに配置して静電制御を強化できます。

MOSトランジスタチャネルは、リン化インジウム(InP)基板上に成長したInGaAs層をシリコン基板上に転写し、Y 2 O 3層でコーティングすることにより構築されました。 InGaAs表面を準備しました。自然酸化物を除去し、アセトン、水酸化アンモニウム、硫化アンモニウムから成る溶液で不動態化しました。 清浄化された表面は、電子ビーム蒸着によって堆積された10 nmのY 2 O 3でコーティングされた。 シリコン基板は、フッ化水素酸で精製した後、10 nmのY 2 O 3でコーティングしました。

ワッフルミックスは、空気中の手動圧力によって達成されました。 InP成長基板とInGaAs保護層は、ウェットエッチングにより塩酸とリン酸を使用して除去しました。 ニッケルと金がソース電極と流出電極に使用されました。 InPはソース領域とアウトフロー領域で部分的にエッチングされたため、完全に除去する必要がありましたが、移動度に影響する可能性のある表面への影響を減らすためにチャネル領域に残りました。

最終的なデバイスは、300 ° Cで急速熱アニーリングにかけられました。シャッターとチャネル(本体)の長さは、厚さ10 nmで2μmでした。 サブスレッショルドの変動は90 mV / 10年であり、研究者はEOTが比較的大きいため「非常に低い」と説明しました。 有効な移動度は、アニーリングしなくても、シリコンベースのデバイスと比較して2.5倍増加しました。 300°Cでのアニーリングにより、実効移動度が2000 cm 2 (V・s)に増加しました。 研究者によると、これらの最初の指標はプロセスの最適化により改善できます。

上記のすべては、実験、革新、新しい高みに到達する試みです。 このプロセスが非常に長く、多くの障害や障害に関連する可能性があることを否定しません。 しかし、これはまさに、時間の経過とともに私たちの生活の不可欠な部分となるイノベーションそのものが生まれる方法です。