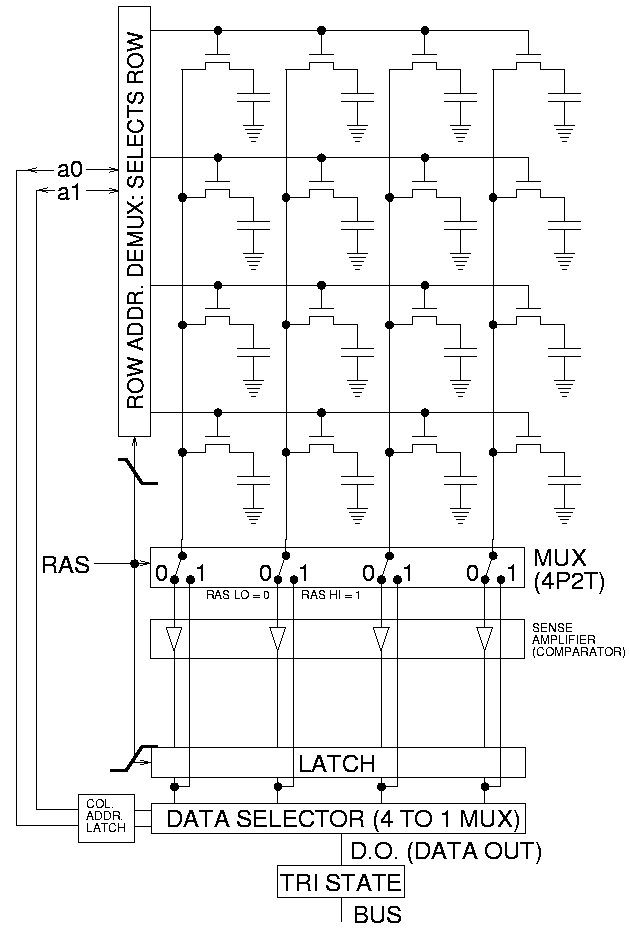

DRAMの構成

DRAMは2次元格子であり、ノードにはメモリセルがあり、各セルに1ビットが格納されます。 各セルはトランジスタと、ビット1または0の値に対応する充電または非充電のコンデンサで構成されます。コンデンサは時間とともに電荷を失うため、情報を定期的に(数十ミリ秒)書き換える(再生)必要があります。 最新のチップでは、いくつかの独立したモジュール(「バンク」)が作成され、パフォーマンスが向上し、出力ステージが分離されています。

情報を読み取るには、対応するトランジスタのラインが開くように、水平ラインの1つ( ワードライン )に電圧が印加されます。 この場合、このラインのセルのコンデンサの電荷は垂直ライン( ビットライン )から読み取られます。 その後、 ワードラインが閉じられ、別の行の読み取りに進むことができます。

ワードラインを定期的にオンおよびオフにすると、誘導電流により同じバンクの隣接セルでリークが増加することがわかりました。再生サイクルを何度も切り替えると、ビットを0から1に、またはその逆に切り替えるのに十分である可能性があります。

デモンストレーション

この効果は、特別な特権を必要としないコードを使用して実現できます。 最も単純な攻撃は次のようになります。

code1a: mov (X), %eax ; X mov (Y), %ebx ; Y clflush (X) ; , X clflush (Y) ; , Y mfence ; jmp code1a

アドレスXとYは同じバンクにある必要がありますが、異なるDRAMラインにあります。 キャッシュリセットは、各サイクルでRAMからの読み取りを保証するために必要です。 各サイクルでワードラインをオン/オフにするために、2つのアドレスを使用する必要があります。 DRAMロジックがワードラインの包含を最適化し、必要な常時切り替えが発生しないため、このコードは脆弱性を引き起こしません。

code1b: mov (X), %eax clflush (X) mfence jmp code1b

エラーを発生させるには、2つの再生成の間の時間(通常は64ミリ秒)で数十万サイクルを実行する必要がありますが、これはかなり達成可能です。 いくつかのビットのエラーが同時によく発生するため、ECCの存在はあまり役に立ちません。