長年にわたり、LSIの専門家は、パフォーマンスを最適化し、寿命を延ばすために、NANDフラッシュメモリと対話するための分析の重要性を理解するようになりました。 この点で、同社はNANDフラッシュの動作を研究し、LSIコントローラーとの相互作用の機能を説明するグループを作成しました。 この分野の専門家、分析部門のチーフエンジニアであるビルハントとのインタビューに注目します。これにより、グループが何をしているのかをよりよく理解できます。

すべてのNANDフラッシュは同じですか?

もちろん違います。 NANDフラッシュの仕様、パフォーマンス、およびその他の特性は、メーカーが異なるだけでなく、同じファミリのモデル間でも異なります。 異なる時期に生産された同じモデルのチップでさえ、特に最初の段階とその後で異なることがよくあります。 製造業者は、たとえば企業やカスタムソリューションなど、さまざまな市場向けに単一のチップのさまざまなモデルを作成することがあります。 NAND型の違いを理解することは、効果的なソリューションを構築するために不可欠です。

異なるメーカーのNANDチップの違いは何ですか?

チップメーカー間の違いには2つの「レベル」があります。アーキテクチャの違いによる違いと、同じアーキテクチャを使用するメーカー間の違いです。 設計と製造プロセスが異なるNANDメーカーにとって、違いは劇的です。 それらは、さまざまなピン配列、電力要件、ブロックとページの配置、アドレッシングスキーム、コマンド、読み取りエラーの回復手順などで構成されています。

一部のメーカーは、同様の設計と製造プロセスを使用しています。 しかし、そうであっても、それらの製品は運用上の大きな違いがあるかもしれません。 生産、コマンド、診断中の設定に応じて、各デバイスに固有のプロパティを設定できます。 ONFIやToggleなどの標準インターフェイスを使用しても、同じ動作が保証されるわけではありません。 各メーカーは、これらの規格について独自の解釈を持っています。

NANDチップの世代間の違いは何ですか?

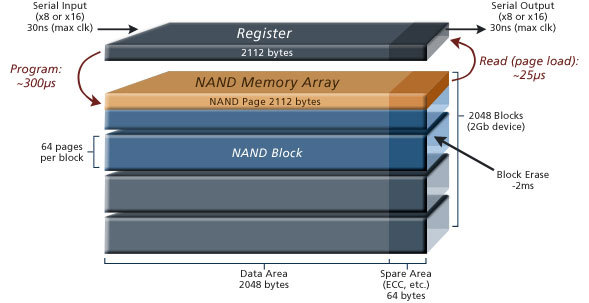

チップ製造で形状を縮小するには、新しいアーキテクチャが必要です。 新しいアーキテクチャにより、NANDデバイスの動作と仕様が変更されます。 最大の変更点は、メモリチップの密度の増加です。 たとえば、ブロックとページのサイズと場所を変更して、新しいアーキテクチャと容量の増加に対応する必要があります。 メモリセルが小さく高密度になると、エラー処理機能も向上するはずです。 エラー訂正コード(ECC)およびスペアエリアの要件は増大しています。 NANDは、不良ブロックの増加する速度にも適応する必要があります。 ユーザーのニーズを満たすために、各新世代のデータ転送速度とパフォーマンスも向上させる必要があります。 これにより、インターフェイスのタイミング仕様が変更され、新しい機能が追加されます。 一般に、NANDのパフォーマンスはジオメトリが高密度になるにつれて悪化するため、より強力で効率的なECCメカニズムを開発するには、これらの変更を理解することが重要です。

LSIフラッシュ分析ラボではどのようなテストが行われていますか?

フラッシュ分析ラボには2つの目標があります。 まず、NANDデバイスをLSI SandForceコントローラーを使用してSSDに統合し、それらが連携して動作することを確認します。 次に、NANDデバイスをテストして、フラッシュメモリのライフサイクル全体の動作を確認します。 さまざまな動作モードでテストを実施しています。 NANDチップの動作を直接理解することは、市場が要求する信頼性とパフォーマンスを備えたソリューションを開発するために重要です。

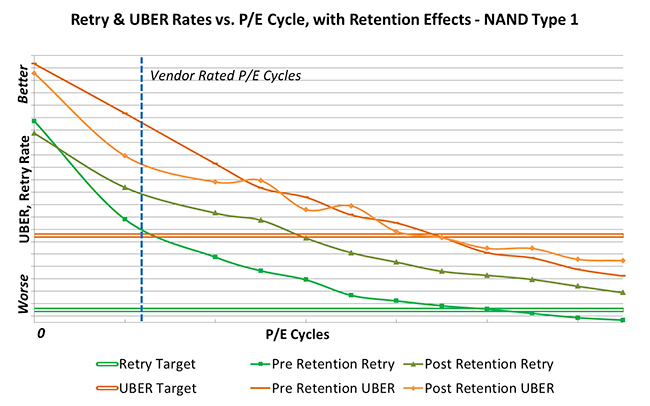

フラッシュメモリテストは、パスポートのライフサイクルの「外部」にありますか?

はい NANDプロバイダーは、耐久テストの結果と方法を常に共有しているわけではないため、このデータを自分で収集する必要があります。 通常、エラーレベルが非常に大きな値に達するか、致命的な障害が発生するまで、書き込み/消去サイクルを実行します。 また、バックアップボリュームなどの他のパラメーターも測定します。 現実のシナリオでデバイスがどのように動作するかを予測するには、メモリの経年変化に伴う動作を理解するだけで十分です。