前のトピックトピック- 「Intel:2007年末までのPRAMの大量生産」

2006年、インテルはSTMicroelectronicsと共同で、30年以上にわたって全体として取り組んできた技術に基づいたメモリチップを実証しました。 最初のチップサンプルはAlverstonと呼ばれます。

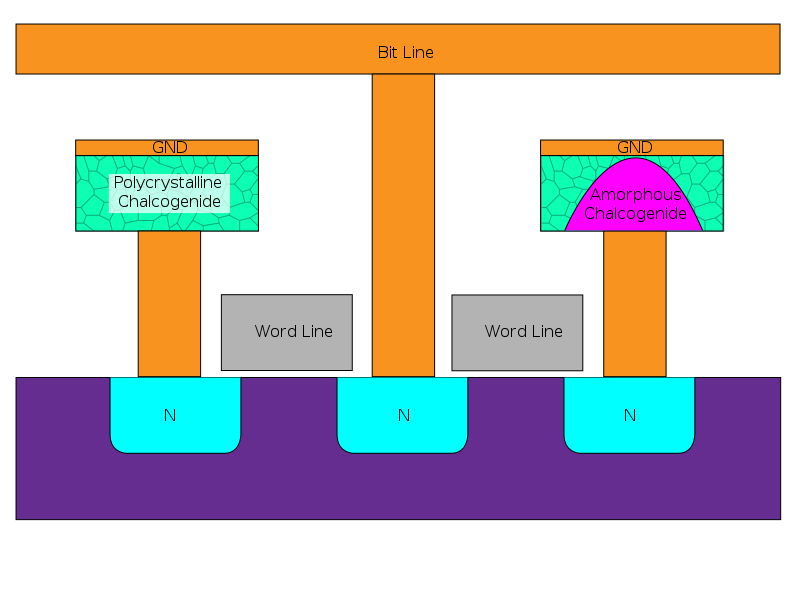

Alverstonチップは、光ディスク( カルコゲナイドガラス )の作成に使用される材料と同様の材料に基づいており、動作原理は相転移に基づいています。

このテクノロジーは30年以上前に1970年に初めて知られるようになりました。1970年、Intelの創立者の1人であるGordon Mooreが「フェーズメモリ」(相変化メモリ)に関する記事を発表しました。

「フェーズメモリ」の動作原理:

材料-カルコゲナイドガラス(GST)、ゲルマニウム(Ge)、アンチモン(Sb)、テルル(Te)で構成されています。 通常の(冷たい)状態では、材料は電気抵抗の高いアモルファスガラス構造です(状態1)。 高温(最大600℃)にさらされると、材料は結晶化するため、結晶化点より高い温度、ただし材料の融点より低い温度に到達することが重要です。その場合、材料の抵抗は非常に低くなります(状態2)。 相転移の結果として、電気特性と光学(屈折率)の両方が変化します。 この移行は5 ns未満で実行できます(2006年のデータによる)。

状態1(不十分な編成)を使用して低レベルの信号を取得し、状態2(厳密に構造化)を使用して高レベルの信号を取得します 。

今年2月、Intelは、相転移技術に基づいてチップの容量を2倍にする開発を発表しました。 以前は、「位相メモリ」は2つの状態(上記)によって実現されていましたが、研究者は、アモルファス状態と結晶状態の間に、情報を保存するために使用できるもう2つの状態があることを示しました。 セルに2ビットを追加することで、IntelはSTMicroelectronicsとともにチップのパフォーマンスを大幅に向上させました。 インテルはすでにフラッシュメモリで同様のトリックを習得しており、メモリセルに複数のビットを保存できるため、「フェーズメモリ」の開発におけるこのステップは驚くことではありません。

「位相記憶」の研究は過去数年で大幅に進歩しており、数年前に大量生産への移行が有望に見えなかった場合、これについて疑いの影はありません。

「フェーズメモリ」の主な利点と違い:

- データを保存するために、電子料金ではなく自分自身の物理的状態を使用する

- DRAMおよびSRAMとしてだけでなく、不揮発性メモリとしても使用できる可能性

- 低消費電力

- クリスタル上により多くの要素を配置する能力、

- 外部の影響に対する高い耐性、

- 耐久性(約1億回の書き換えサイクルに耐え、さらにゆっくりと劣化する)、

- より高い書き込みおよび読み取り速度。

記事に基づく: