この記事では、FPGAの開発における私の経験について話し、プロジェクトを紹介します-公式に従ったビデオジェネレーターです。

投稿目的

私はC ++プログラマであり、システムソフトウェアの開発と保守に専門的に従事しています。 約2年前、私は回路を研究するか、Verilog言語を使用してFPGAをプログラミングすることにより、経験を多様化したいと考えていました。 次に、その由来を説明します。

仕事の目的

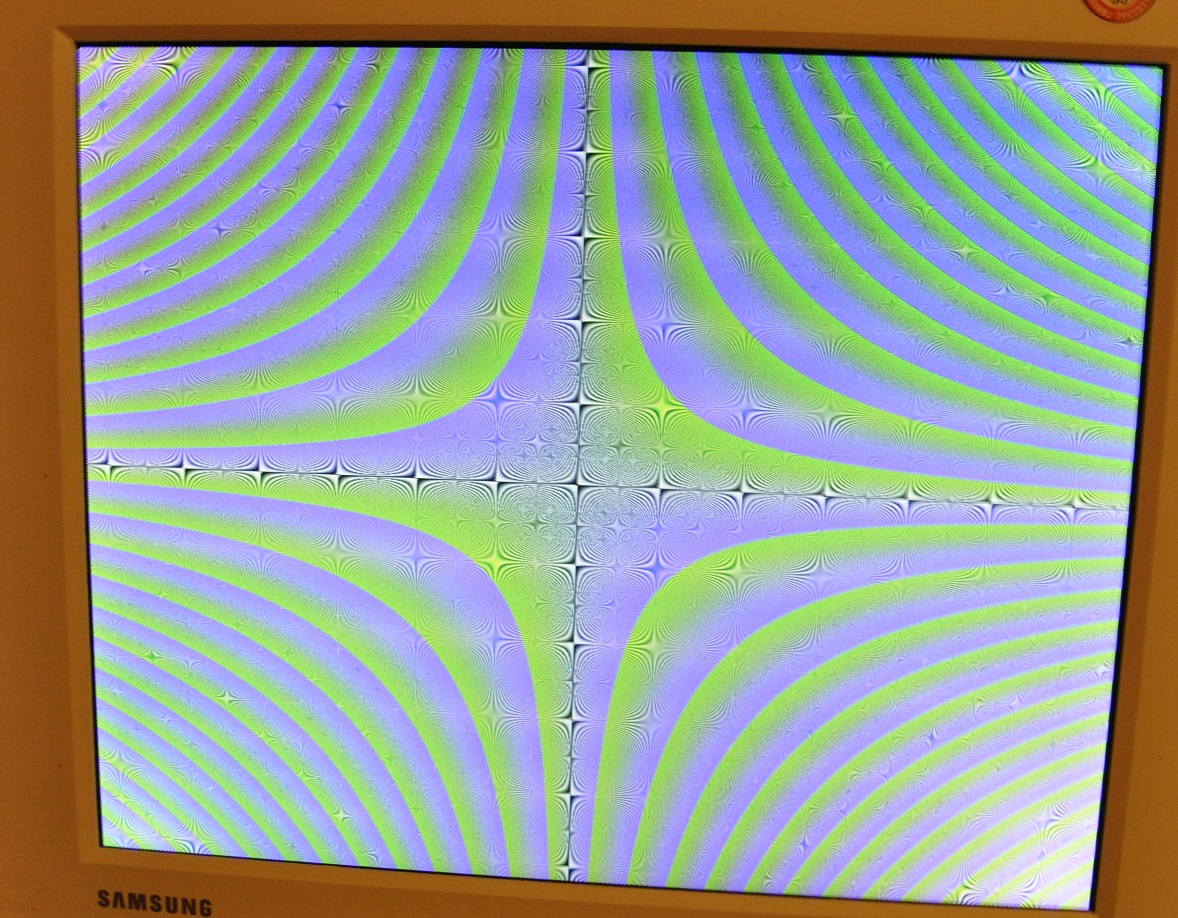

ジェネレーティブアートのニーズにFPGAコンピューティングパワーを向けるには、高フレームレートで高解像度の複雑な数式を使用して、リアルタイムストリーミングビデオを生成します。 IBNIZは 、デモシーンの仮想プラットフォームとしてviznut 同志によって開発された、デモを生成するための式を記述するための言語であるフロントエンドとして選択されました。 以前は、FPGA、プラットフォーム「 Mars rover 」、 彼の発見の1つに実装していました。

理論

回路とプログラミング

私の意見では、プログラマー用の回路は開発に関連する興味深い分野です。 機器の説明は、一方では入力を容易にするプログラムの作成に多くの点で似ていますが、他方では、適用された問題を解決するまったく異なる方法を定義し、エンジニアに新しい機会と経験を与えます。 通常、1行ずつ順番に機能するプログラムを作成します。 すべての部分が同時に機能するプログラムを作成しようとすることは有益です。

したがって、これは興味深いですが、実現可能性について考えてください。 FPGA上のソリューションが正当化されるタスクを選択する方法は? 第一に、場合によっては、回路設計はソフトウェアよりもエレガントで信頼性があります。 たとえば、私はマイクロコントローラーでsumotボットをプログラムし、彼に最も単純な音声を作成しました。スピーカーは出力の1つに掛けられ、その信号はオーディオ周波数によって変化します。 すべては単純です-サイクル、内部の切り替え、遅延。 しかし、ビープ音の間にロボットが停止しました。 同時に動作するには、マルチタスクが必要であり、ディスパッチャを記述する必要があります。ディスパッチャは、複雑さが増すとリアルタイムOSに変わります。 FPGAソリューションでは、中央コンピューターのリソースを共有する必要はありません。スピーカー制御サブシステムは一部のFPGAを使い果たし、誰も気にしません。

第二に、特殊な回路は、ソフトウェアソリューションよりもはるかに高いパフォーマンスを実現できます。 1280x1024 @ 60Hzのビデオストリームをリアルタイムでピクセル単位で処理するには、8,000万を処理する必要があります。 1秒あたりのドット数は、強力なプロセッサでも時間はあまりありません。回路ソリューションは、より豊富な機会を提供します(アルゴリズムの特定の制限の下で、処理はステレオタイプである必要があり、ブランチは望ましくありません)。

HDL

FPGAのプログラミングには、VerilogやVHDLなどの特別な言語を使用できます。 私の意見では、それらは回路エディタよりもはるかに便利ですが、高度なプログラミングに慣れている人は残念です。 私の経験は(システム)Verilogを使用していますが、私が知る限り、VHDLはそれほど違いはありません。 回路はレジスタ転送レベル(RTL)で記述されますが、これは自然なように見えますが、記述は2つの部分に分かれています:組み合わせ回路と同期論理です。 たとえば、ループ演算子があり、列による除算を記述しますが、結合部分はループ本体内では記述できず、同期のみであることがわかります。 マクロがあります。ベリログのマクロ言語は、「#」を「」に置き換えるまでのC番目のプリプロセッサです。 さて、モジュールは数値パラメーター(コンパイル時間)を持つことができます。これはおそらく、私たちの兵器庫での一般的なプログラミングのすべての手段です。

RTL同期回路

ほとんどの場合、電子回路設計者は同期回路に限定されています。 つまり、共通のクロック信号(クロック、クロック)があり、説明は多くのレジスタと、次のメジャーのレジスタの値が前のレジスタの値に依存する方法を決定する組み合わせ回路に分割されます。 組み合わせ回路には独自の状態がありません。 マイナスは自由の制限です。たとえば、非同期回路を使用した乱数ジェネレーターの実装の説明に会いました。 一般に、FPGAアーキテクチャは同期回路でのみ動作するように設計されており、PLL(PLL)などの基本的に非同期のモジュールは個別のハードウェアユニットとして実装されます。

PLLを使用すると、たとえば、コンピューティングモジュールをビデオアダプターから分離して、それぞれに固有の周波数を持たせるために、いくつかの「ブロックドメイン」を作成できます。 非同期回路は、私が理解しているように、回路技術者はおおよそ自己修正コードについてのプログラマーに似ています。

回路が動作できる周波数は、主に回路自体に依存しますが、FPGAのタイプにも依存し、その「速度クラス」が役割を果たします。 意味は次のようなものです。1クロックサイクルで、信号が回路の最長パスに沿って実行され、ターゲットレジスタを切り替える時間が必要になります。 説明したソリューションの頻度を超えると、特徴的な鼻水が画面に表示されました。

鉄

プロジェクトは、4つのデバッグボード、 Terasic DE0、Terasic DE2-115、VGAの代わりにLTMディスプレイを搭載したTerasic DE0-nano、およびRover II用に準備されました。 Terasicには優れたハードウェアがあり、ソフトウェアはそれほどバラ色ではありません。 ドキュメントとサンプルの例がありますが、必ずしも十分ではありません。 たとえば、FPGAを直接フラッシュする方法を既に学んだので、同じファームウェアをコンフィギュレーションメモリ(eeprom)に駆動しようとして1日を殺しました(ボードがオンになったときにこのファームウェアがロードされるように)。 もう一つの問題は、ロシアではリーズナブルな価格でそれらを見つけるのが難しく、台湾人はそれらを普通郵便で送らないことです。 Mars rover IIの機能は劣っていますが、説明とサポートの方がはるかに優れています。彼らのサイトの記事では、次の困難に対する解決策を見つけました。 私の最初のデバッグボードは、最初の火星探査機でした。機能は劣りますが、上記を習得することは非常に簡単です。

ツールキット

私はALTERAベースのデバッグボードを使用していたため、無料のWebエディションであるQUARTUSが開発環境として機能しました。 QUARTUSは複雑な印象を残します。 主な不満は非常に直感的で、文書化が不十分で、チュートリアルはありません。 同時に、彼は統合開発環境の義務を果たします。 これはFPGAを使用する場合の典型的な状況です。作業は機能しますが、利便性(開発の容易さを含む)は最後になります。原則として、ここでは愛好家は期待できません。

実装

そのため、機能ごとにビデオを生成します。 ibniz、またはむしろその「線形」サブセットが仕様として機能します。 利点は、第1に、既製のデモを借りることができ、第2に、 リファレンスソフトウェアの実装で作業した結果を比較できることです。

作業は主に2つの部分に分けられました。データを準備し、結果をディスプレイとカーネルに表示するインフラストラクチャです。カーネルは個々の基本ibniz関数を実装します。

主なインフラストラクチャコンポーネントはVGAアダプターです。 通常のアプローチは、フレームバッファを使用することで、外部メモリを使用します(内部メモリでは不十分です)。 これによりプロジェクトが複雑になり、メモリを他のものに使用できなくなります。 したがって、カーネルはVGAと同期して動作し、ピクセルの色が計算されてすぐに描画されます。

短所:

コアに課されるVGA周波数

VGAが「画面の見えない部分」を満たす間、コアはアイドル状態です。

ハードリアルタイム。クロックサイクルごとに別のピクセルを与える必要があり、そこに保存して、後でここで使用できないようにします。

フレームバッファに直接書き込むためのibniz命令は、遷移演算子と同様に実現不可能です。

利点:

実装のしやすさ

メモリが引き出さないチャネル幅を使用できます。

メモリは他の何かのために保存されます(ここでリソースを共有することはほとんど不可能です)。

レイテンシーが低く、意味はほとんどありませんが、カメラ信号があれば美しいですが、これは別のプロジェクトです。

真の60Hzビデオは目を楽しませます。

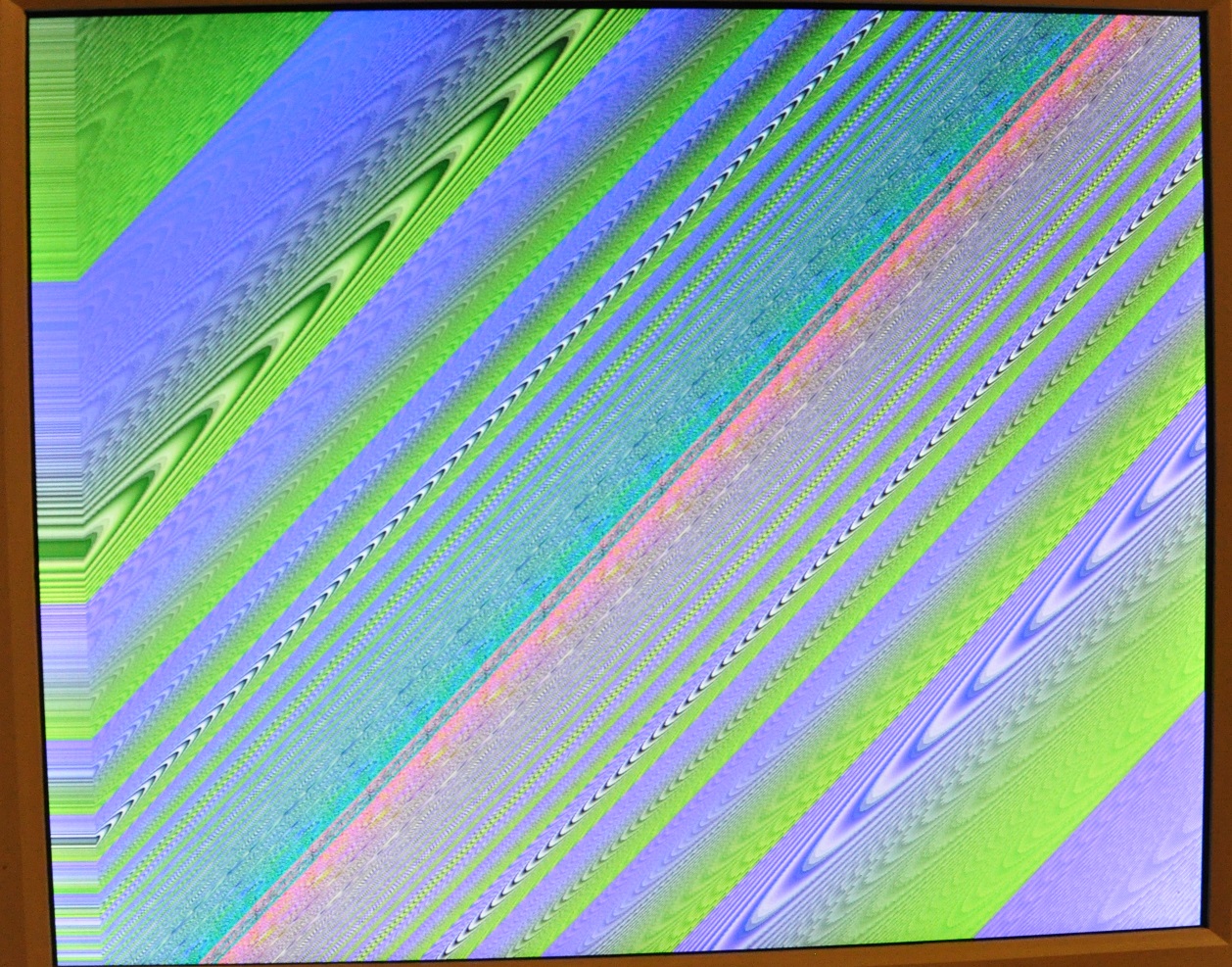

コア

プロジェクトの中心は数学関数-sin、atan2、log、sqrt、および除算で構成されています。 デジタルツーデジタルアルゴリズム( CORDIC )を使用して自分で実装しましたが、利点はソフトウェア実装の経験でした。 これらは反復アルゴリズムであり、反復回数は引数の容量に比例します。 反復はサイクルごとに行われます。つまり、引数の到着から結果の入力への出力、ビット数に等しいサイクルパスの数、ibnizの場合は32です。サイクルごとのポイントを考慮する必要がある場合、これをどのように試せますか? コンベアの助けを借りて、コンピューティングユニットは32(ハードウェア)ステージで構成されています。 遅延があり、ブロックのシーケンスでは遅延が累積します。 それに対処することは難しくありませんが、明確にするために残しました。その結果、画像が右にシフトし、左端に沿ってアーチファクトストリップが表示されます。その幅は、特定の例のコンベヤーの深さ全体に対応しています。

かわいらしさ

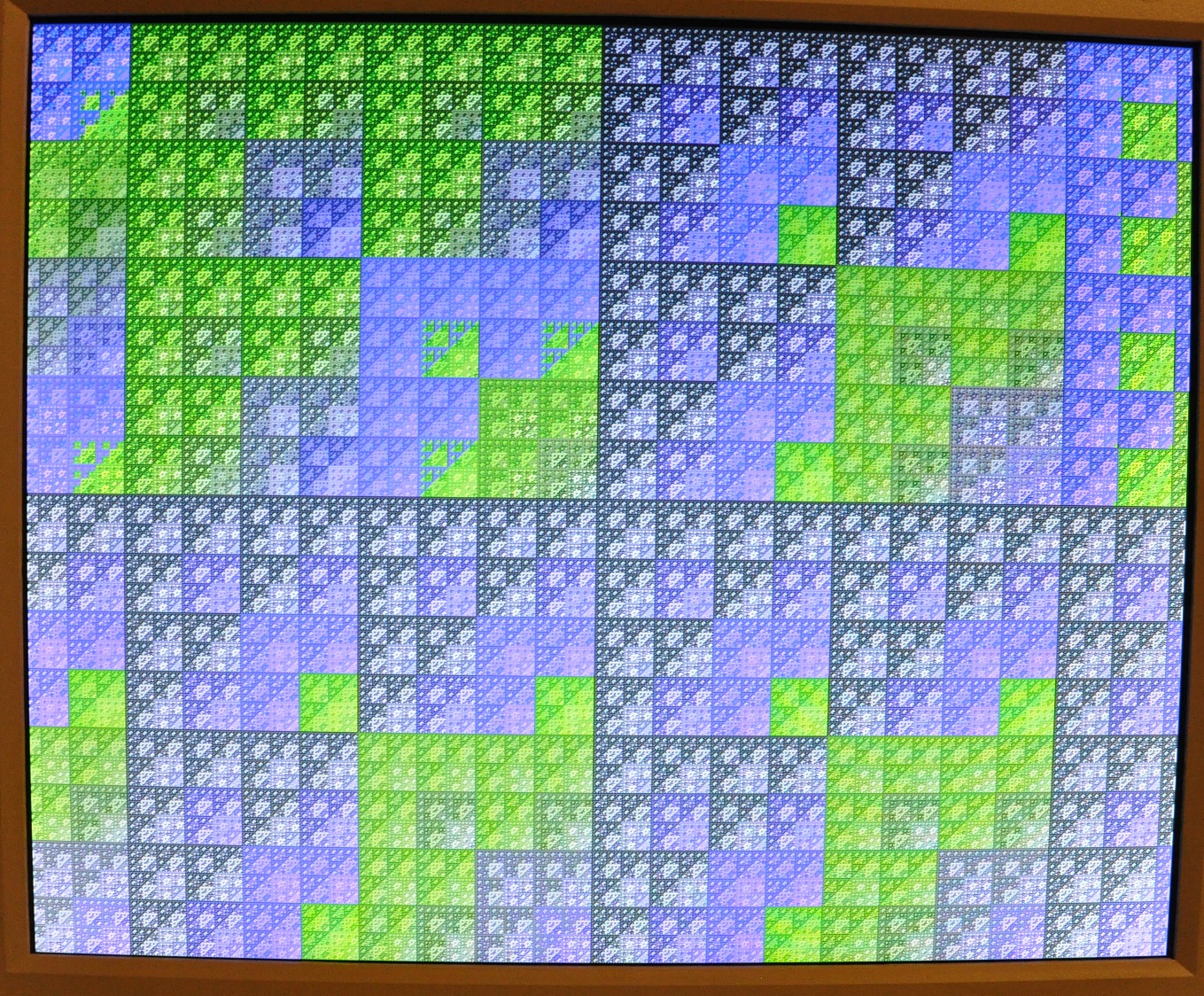

Habréのジェネレーティブアートについては、たとえばここで 、 たとえば私の5kopについて既に書いています。 コンピューターで画像を生成し始めると、最初は異常なもの、つまり逆説的な形、酸味に明るい塗料を探します。 しかし、そのような「作品」はすぐに退屈します。 興味深いこと-多様性を高めるには、制限を課す必要があります。 「ランダムな」画像は平らに見えますが、特定の形状に引っ張ることでボリューム感を加えることができます。 Jupiterデモでは、中間のテクスチャ画像が球に重ねられます。 これを行うには、 この記事で説明されているように、デカルト座標から球座標への座標変換も使用します 。 ボリュームの感覚は、照明だけでなく動きによっても強化されます。4つの円球のデモをご覧ください。

まとめ

それでは、プログラマーは回路に入るべきでしょうか? 重大な意図がある場合にのみ、少なくとも目的を正確に知る必要があります。これは、低レベルの作業、洗練されていない開発ツール、および明白でないプログラムロジックによって引き起こされるエネルギー消費型ビジネスであるためです。 スケールの反対側には、新しい機会と経験があります。 説明したプロジェクトに加えて、 手順の音楽ジェネレーター 、 MIDIシンセサイザー 、およびビデオカメラからの信号フィルターも作成しました 。

今、私はプログラムモデルを考えて書く段階で、もっと深刻なプロジェクト、つまり組み合わせ論理に基づいた非ニーマンコンピューターを作成しています。 主なアイデアは、機能プログラムの動的ツリーは、鉄に縫い付けられた静的で大きな通常のグラフ上に存在し、可能であればツリーの枝が同時に進化するということです。 ノードは可能な限りシンプルで、コンビネーターのみを使用できます。 教会の数字のみの形式の整数。 利点は、純粋な機能スタイルで単純なシンボリック操作を大量に実行することです。 正規表現の解析や推論のようなものかもしれません。 もちろん、実際の作業の大部分では、従来のアーキテクチャを追い越すことはできませんが、少なくとも1つの適切な領域を突然見つけた場合、あなたは見て、シリコンに到達します。 さて、または少なくとも、アセンブリ言語としてunlambdaを使用するアーキテクチャがあります。

`` `s``s``sii`ki

`k。*` `s``s`ks

`` s`k`s`ks``s``s`ks``s`k`s`kr``s`k`sikk

`k``s`ksk