はじめに

数日前、AMD(Am386-DX)のプロセッサを搭載した4メガバイトのRAM、VGAビデオカード、およびドライブコントローラー、ハードドライブ、パラレル、シリアルの機能を実行するマルチカードを搭載した最初のコンピューター、386ポート。

もちろん、彼は長い間彼のケースと古代の死んだハードから免れていました-今では彼は一対の拡張カードを備えたマザーボードでした。 数年前、新しいハードディスク10 GB(当初は200 MBのディスクしかありませんでした)に接続し、そこにFreeDOSをインストールしました。

しかし、今回、彼はBIOSよりもさらに起動することを拒否しました-音で判断すると、クローゼットに横たわっている数年間は10 GBが200メートル後に追い詰められました。

そして、私はこのコンピューターで何かをしたい、この古さを触りたいという強い欲求に目覚めました。それにより、ユーザーとしてではなく、開発者として既にITに精通し始めました。 理想的には、もちろん、SDカードで動作するハードドライブエミュレータを作成したいと思いますが、徐々にこの目標に向かっていきます。 簡単なタスクから始めましょう。実際のハードディスクコントローラと並行してハングし、データ交換を記録するデバイスを組み立てて、古いBIOSがハードドライブを検出する方法を正確に調べます。 最初は同じことをするつもりでしたが、フロッピーコントローラーについては、最後のハードダイの後、BIOSだけが残っています。BIOSはフロッピーをチェックしません。 しかし、彼はハードドライブに関連するいくつかの項目を持っています-ハードドライブの検出とそれらをフォーマットするための手段。

もちろん、これはFPGAのアーキテクチャにより非常に簡単に行われますが、予算オプションに固執し、STM32F103コントローラーといくつかのディスクリートロジック回路でこれを実行しようとします。 それでは、始めましょう。

鉄

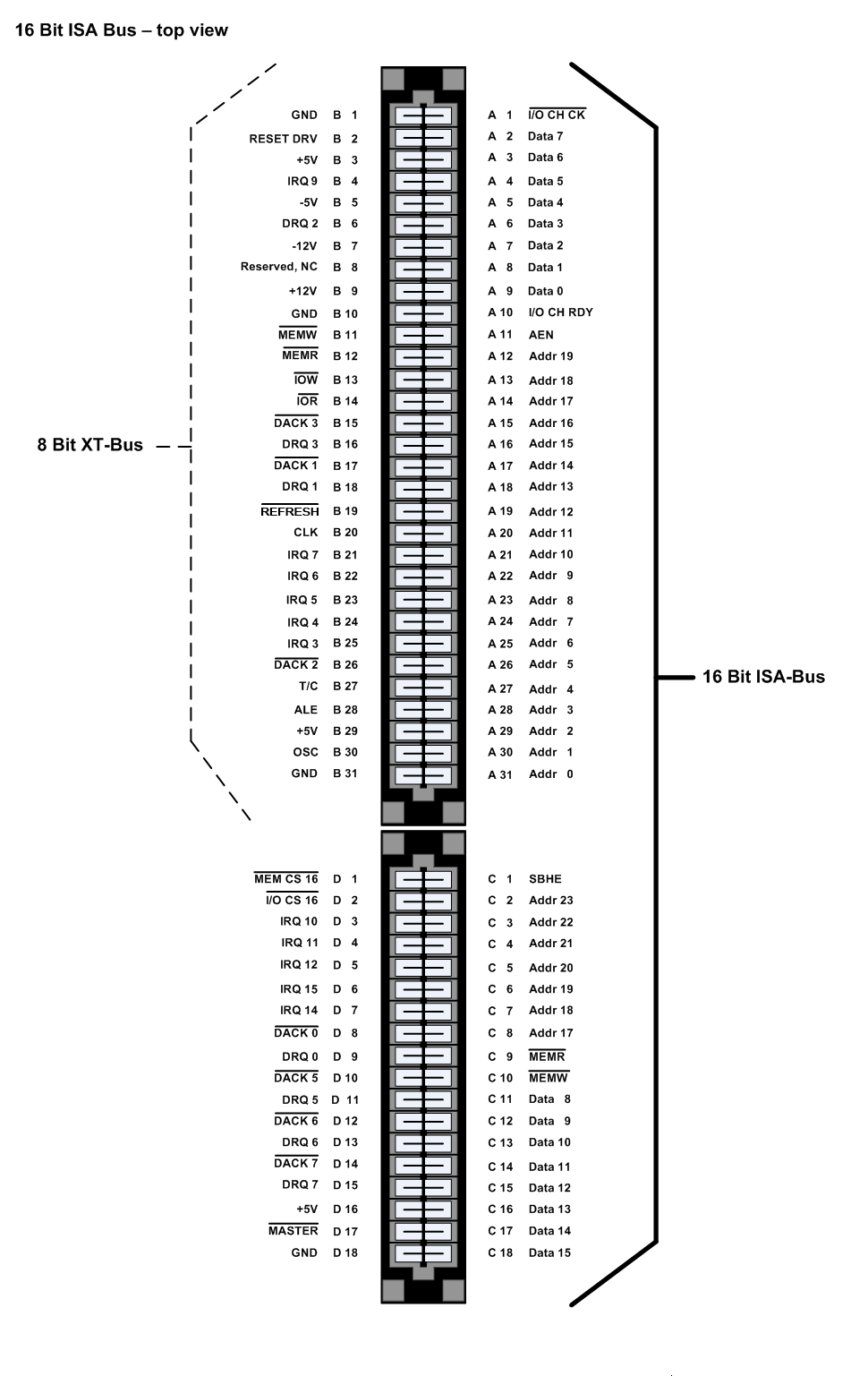

伝統的に、私たちは広葉樹の底から行きます。 古いコンピューターの基礎となるISAバスとは何であるか、そしてどのように接続できるかを正確に思い出しましょう。 x86マシン内の回路を実際に理解していない人にとって、これはそのようなシステムのアーキテクチャを明らかにするのに役立ちます。 実際、すべてが非常に単純です-「クリーンな」ISAにはプラグアンドプレイツールはありません-それらは次の標準でのみ登場しました。したがって、デバイスにアドレスを発行する手段はありません。

したがって、ISAカードは、ハードウェアで指定されたアドレスを持つデバイスです(ジャンパーでベースアドレスを選択する機能を備えた、厳密に定義された回路)。 バス自体には、20本のアドレスライン、16本のデータライン、複数の電源信号、複数のIRQライン、および一連の制御信号が含まれています。

どのように機能しますか? デバイスのいくつかのLEDをオン/オフする機能が必要だとします。 これを行うには、たとえば74HC273などのISAボードにレジスタチップを配置します。

これは最も一般的な8ビットの「ラッチ」であり、信号によって入力に供給されたものを記憶します。 レジスタの出力をLEDに接続し、それらを忘れてください。 ソフトウェアの観点から見ると、ISAバス上のデバイスとの対話は2つの方法で実装できます。

- メモリマッピングの助けを借りて、メモリの読み取り/書き込み信号をデコードし、DRAMコントローラーではなくバスに結果を出力します。これがビデオカードの動作です。ビデオメモリはコンピューターのメモリのアドレス空間にマッピングされます。 したがって、コンピューターのビデオカードのメモリへの書き込みは、そのRAMへの書き込みと変わらず、通常のMOVコマンドによって実行されます。

- 大きなデータブロックを転送する必要のないデバイスには、いわゆる「I / Oスペース」が使用されます。これは、周辺デバイスに割り当てられ、16アドレスビットに制限された別個のアドレススペースです。 INおよびOUTコマンドによってアクセスされます(I / Oポートへの読み取りおよび書き込み)

実際、「別個のアドレス空間」という言葉の背後には物理的に単純なエンティティがあります。ISAバスには、 MEMW、MEMR、IOR、IOWという4つの信号があります。 コマンドを実行してメモリの読み取り/書き込み( MOV )またはIOの読み取り/書き込み( IN 、 OUT )を実行すると、目的のアドレスが同じバス、ラインA0〜A19 ISAに設定されます。 データは同じ行D0-D15にも沿っています。 唯一の違いは、メモリから読み取る場合、 MEMRラインでアクティブレベルが設定されること、メモリへの書き込み-MEMW 、IOポートからの読み取り-IOR 、書き込み-IOWの場合です。

したがって、1つのレジスタとLEDを備えた最も単純なデバイスを作成するには、必要なアドレスがバスに設定されているかどうかを判断する必要があります(誰もアドレスを提供しないこと、既存の周辺機器と競合しないアドレスを選択する必要があることを覚えています) IOW信号で、レジスタのラインD0〜D8からのデータの記録を有効にします。

複数のレジスタを含むより複雑なデバイスでは、デバイスの「ベース」アドレスと一致したときに、シニアアドレスラインがデコーダに送られ、アクティブな出力信号を形成します。

より具体的な例に移りましょう-ATAコントローラ。 その作業の原則をよりよく理解するために、OSDev wikiの記事を読むことをお勧めします。

これは9つのIOレジスタによって管理され、そのうち8つはベースアドレス0x1F0から順に並んでいます。 残念なことに、9番目は0x3F6にあり、デコードスキームをやや複雑にします。

もちろん、コントローラー上のすべてのアドレスラインを取得してデコーダーを作成することはありません。そうしないと、8 MHzバスのクロック周波数、IOサイクルは仕様に従って4サイクル続き、72 MHzで36クロックサイクルしか得られません。考えのために。 したがって、安価なディスクリートロジックチップを使用します。

0x3F6に突き出ているこの9番目のレジスタがなかった場合、ラインA9とA3にゼロが設定され、 A4-A8に 1が設定されている場合(つまり、アドレス0x1F( ..) )。 ISAカードのA9より古いビットは通常デコードされず、上記のアドレスにある同じデバイスへのアクセスの可能性に注意を払いません。

3つの最下位ビットの処理は、すでにコントローラーに委ねられている可能性があります。 残念ながら 、まだ到達していないレジスタ0x3F6があります。

これらのビットは0x1F(..)と0x3F6の 両方に対して示された状態にあるため、初期条件(アクティブラインA4-A8および非アクティブA3 )は常に満たされています。 条件が追加され、次のように定式化できます。アクティブなA9を使用-A1およびA2 (アドレス0x3F6 )にアクティブなレベルが必要です

つまり、

CS0 = A8 & A7 & A6 & A5 & A4 & ~A3 CS1 = A1 & A2 & A9 CS2 = CS0 & (~A9 | CS1)

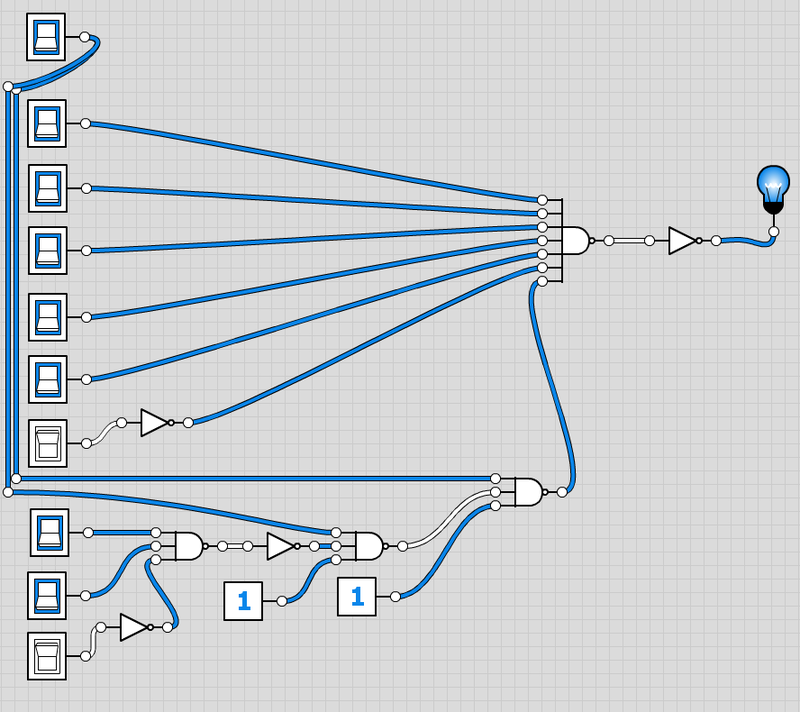

Logic.Lyオンラインロジック回路シミュレータを使用して、私は持っていたマイクロ回路-74HC04(クワッドエレメントNOT) 、74HC30-8入力NANDおよび74HC10(トリプル3入力NAND)に基づいてこの回路を構築しました。

ORエレメントがないため、De Morganのルールを思い出してください-論理積の否定は否定の論理和であり、論理和の否定は否定の論理積、または論理的等式の形です

~(A&B) = ~A | ~B ~(A|B) = ~A & ~B

これを使用します。

~( ~ (~A9 | CS1))) = ~(A9&~CS1) - = (A9 NAND ~CS1) CS2 = CS0 & (A9 NAND ~CS1)

また、純粋なANDがないため、そのコンポーネントを3入力NANDブロックに供給し、ドロップオフ割り込みに入ります。

ご覧のとおり、すべてのロジックは3つのケースに正確に適合しています。

IORまたはIOWのアクティブレベルの存在は、これらの条件に追加されます(標準に従って、アクティブレベルが低いことを忘れないでください。つまり、すでに信号を反転しています〜IORおよび〜IOW )。

CS = CS2 & (IOR | IOW) (IOR|IOW) = ~(~(IOR & IOW) ) = ~(~IOR & ~ IOW) = (IOR NAND IOW) CS = CS2 & (IOR NAND IOW)

最終的な図は次のようになります。

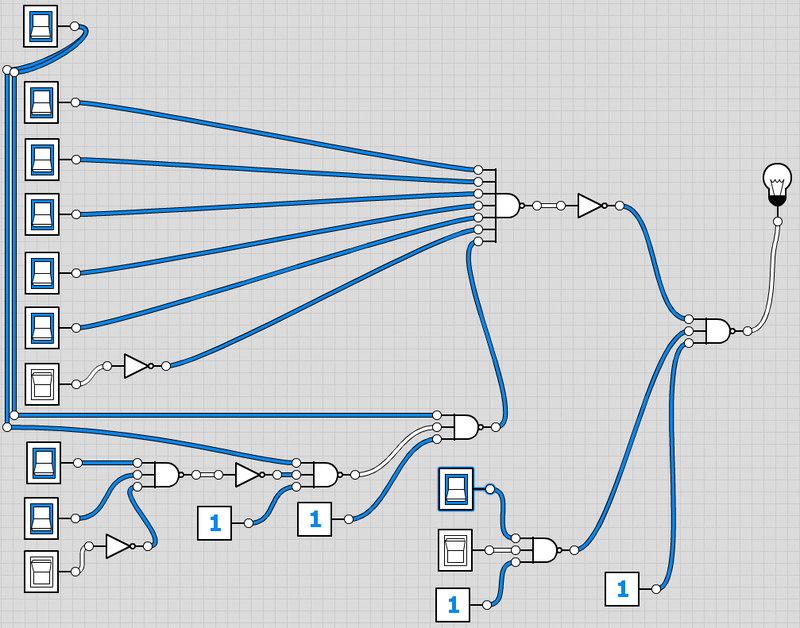

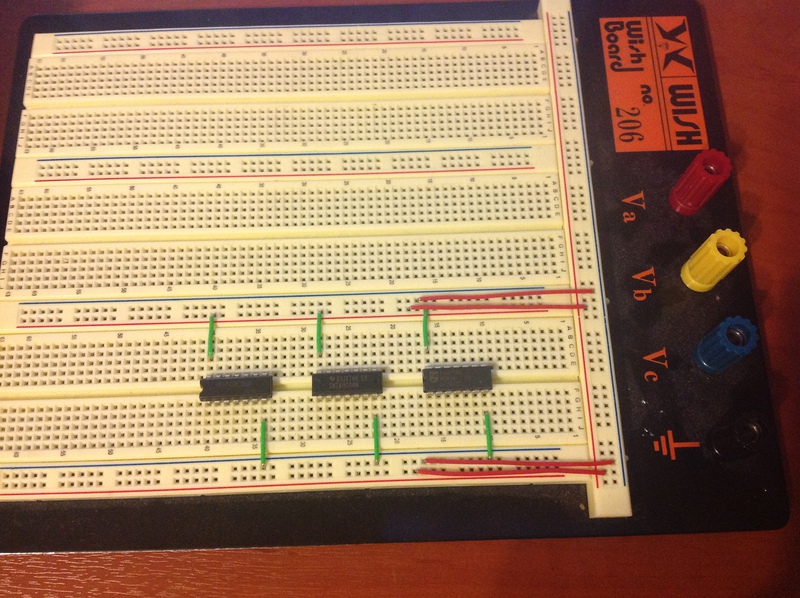

今、モックアップを使用して、鉄でそれを集め始めます。 まず、最初の3つのマイクロ回路を配置します。この回路には、ほとんどの入力信号が送られ、電源バスとグランドバスへの接続に注意します。

出力回路を慎重に追加してから、十分に長いプローブの形式で入力回路を追加します。これは後でコンピューターのマザーボードに接続します。

便宜上、左側の上位アドレス入力( A3-A9 )、右側の下位アドレス入力( A0-A2 )を一時的に修正し、中央でCS2信号を出力しました。

アセンブリから一時的に注意をそらし、オシロスコープで何が起こったかを見てみましょう。 したがって、アドレス入力をバスに接続します-ISAはまさにバスであるため、ATAコントローラボードが挿入されているのと同じスロットにプローブを接続する必要はありません。便利なものを選択します。 残念なことに、プローブはそのような穴には小さすぎたので、上にまっすぐなピンの櫛を貼り付けました-個別に、プローブとピンは脱落しますが、それらは非常にうまくくっつきます。

また、グランドと回路電源をISAに接続することを忘れないでください-同時に-オシロスコーププローブのグランド。

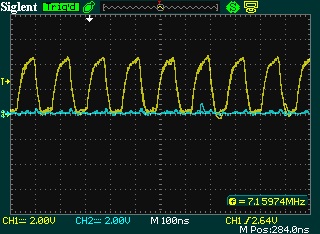

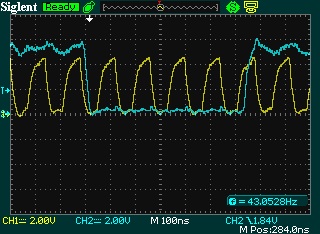

オシロスコープとコンピューターの電源を入れ(すぐにBIOSセットアップメニューに入った)、 CLK信号を確認しました。 次のようなものが表示されるはずです。

もちろん、これは通常8 MHzの周波数のバスクロックです。 私のマザーボードでは、周波数は7.19 MHzであり、BIOS設定に反映されています。 どうやら、これは鉄の機能です-BIOSはこの周波数を下げることを許可していませんでした、または少なくとも正確に8 MHzに設定し、頑固に7.19 MHzを設定しました。 まあ。

回路の入力の接点を確認します。システムが常に異なるアドレスとポートにアクセスするため、それらのいずれかを突くとオシロスコープ画面にカオス信号が表示されます。 そのため、入り口に沈黙がある場合は、連絡先が落ちたことを意味し、再確認する必要があります。

次に、 CS2信号に接続し、次の図を確認します。

IORおよびIOW信号はCS2の形成に関与しないため、バス上のアドレスが指定したアドレス( 0x1F0-0x1F7および0x3F6 )と一致するとアクティブになります。 システムは通常のDRAM再生成を実行するため、美しい周期信号を取得します。 今こそ、オシロスコープの掃引とレベルを調整して、すべての栄光の信号を見るときです。

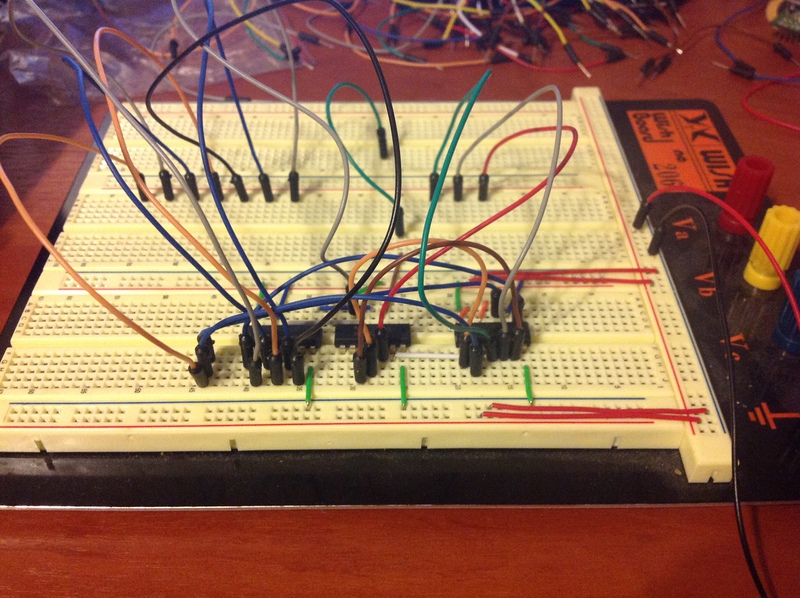

すべてが機能することを確認した後、回路の電源を切り、最後まで終了して、次のようなワイヤのハッシュを取得します。

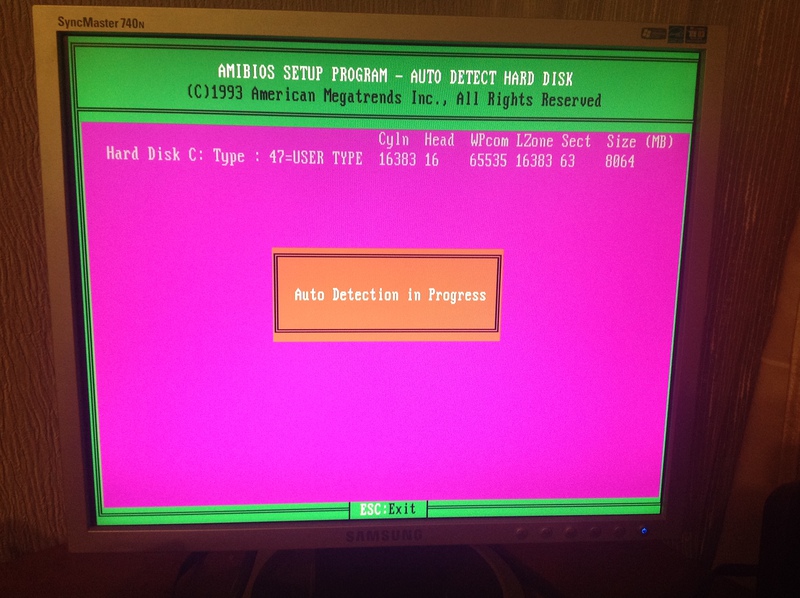

コンピューターの電源を再び入れ、BIOSセットアップメニューに移動し、オシロスコープの電源を入れます。

信号なし! さて、計算の正確さを確認する時が来ました-「ハードドライブの自動検出」項目を選択します。 最初のディスクはすぐに検出されます。おそらく、オシロスコープの画面では、シングルモードをオンにしない限り、何にも気付く時間はありません。

しかし、2番目のディスク(存在しないため)は、コンピューター画面でこれを確認するのに十分な時間検出されます。

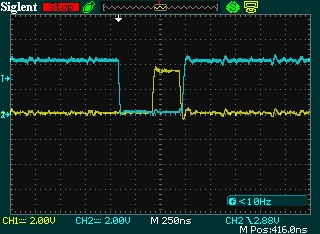

そして、オシロスコープ画面で-これ:

正しいことを確認するために、ディスク検出を終了し、シングルモードオシロスコープをオンにして、画面を注意深く見てください-何もありません! どれだけ待っても、 CSはアクティブになりません! しかし、ディスクの検出に入るとすぐに、標準と完全に一致するおなじみの画像を再び取得します。最後の4クロックサイクルのI / Oサイクルです。

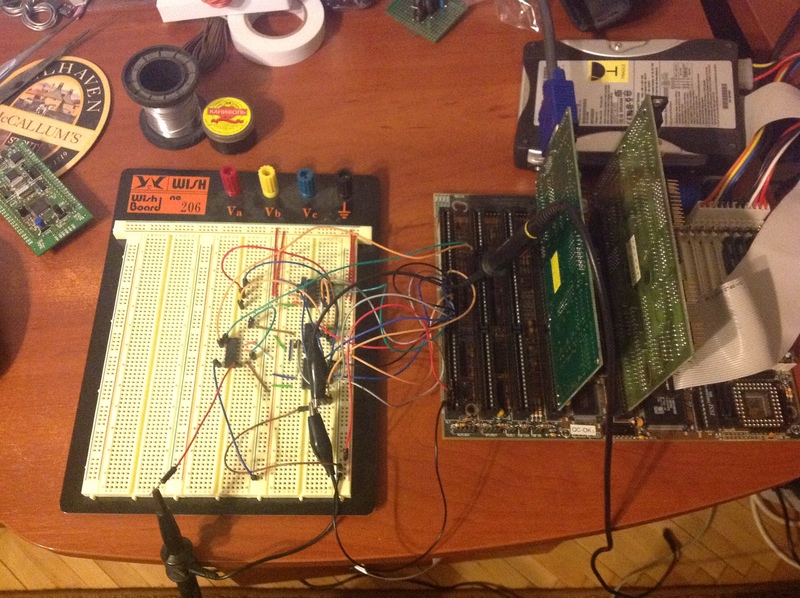

さて、STM32でボードを取り、システムに接続する時が来ました!

私は次のように接続しました:

GPIOD.0-GPIOD.7に接続されたISAデータバス( D0-D7 )

3つの下位アドレス行( A0-A2 ) -GPIOD.8-GPIOD.10 、

アドレスA9の行はGPIOD.11です (結局、このビットは、呼び出しが0x1F6ではなく0x3F6に行くことを理解するために必要です!)

GPIOD.12およびGPIOD.13へのIOWおよびIOR行。

CS信号-GPIOB.0へ

これで、 GPIOB.0で中断する場合、 GPIOD-> IDR (入力データレジスタ)を読み取るだけで、下位8ビットが目的のデータになり、次の4ビットがアドレスになります(さらに、ポート0x1F0に対応する組み合わせは0000-0111および1011になります) -0x1F7および0x3F6 )、次の2つ-モード別( 01で読み取りまたは10で書き込み)。

ここで次のことに注意することが重要です-無効な状態にあるモードビット-00または11で突然結果が得られた場合、これは動作エラーを通知します-この事実はすぐに役立ちます。

したがって、ソフトウェアに渡します。

ソフトウェア

ソフトウェアを使用すると、すべてが非常に簡単になります。入力用のGPIODとGPIOB.0を構成し、 GPIOB.0に接続されたEXTIラインでドロップ割り込みを構成します。

割り込みハンドラーでは、 GPIODから値を読み取り、バッファーへのポインターをインクリメントするだけです。 このバッファーは、任意のインターフェイスを介して分析のためにコンピューターに送信することも、まったく気にせずにデバッグで直接確認することもできます。

セットアップコードを以下に示します。

GPIO_InitTypeDef GPIO_InitStructure; EXTI_InitTypeDef EXTI_InitStructure; RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOD|RCC_APB2Periph_GPIOB|RCC_APB2Periph_AFIO, ENABLE); GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IPD; GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0|GPIO_Pin_1|GPIO_Pin_2|GPIO_Pin_3| GPIO_Pin_4|GPIO_Pin_5|GPIO_Pin_6|GPIO_Pin_7 |GPIO_Pin_8|GPIO_Pin_9|GPIO_Pin_10|GPIO_Pin_11| GPIO_Pin_12|GPIO_Pin_13; GPIO_Init(GPIOD, &GPIO_InitStructure); GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IPU; GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0; GPIO_Init(GPIOB, &GPIO_InitStructure); GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP; GPIO_InitStructure.GPIO_Pin = GPIO_Pin_2; GPIO_Init(GPIOB, &GPIO_InitStructure); GPIO_EXTILineConfig(GPIO_PortSourceGPIOB, GPIO_PinSource0); EXTI_InitStructure.EXTI_Line = EXTI_Line0; EXTI_InitStructure.EXTI_Mode = EXTI_Mode_Interrupt; EXTI_InitStructure.EXTI_Trigger = EXTI_Trigger_Falling; EXTI_InitStructure.EXTI_LineCmd = ENABLE; EXTI_Init(&EXTI_InitStructure); NVIC_InitTypeDef NVIC_InitStructure; NVIC_SetVectorTable(NVIC_VectTab_FLASH, 0x0); NVIC_PriorityGroupConfig(NVIC_PriorityGroup_0); NVIC_InitStructure.NVIC_IRQChannel = EXTI0_IRQn; NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0; NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0; NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; NVIC_Init(&NVIC_InitStructure);

そして、ここに割り込みハンドラコードがあります。

uint16_t Log[1024]; uint16_t ptr=0; void EXTI0_IRQHandler() { Log[ptr]=GPIOD->IDR; ptr++; EXTI_ClearITPendingBit(EXTI_Line0); }

テスト、デバッグ、仕上げ

私たちがやったことを確認する時が来ました! コンピューターを起動し、BIOSセットアップに進みます。 STMkiデバッグを実行します。 ディスクの検出に入り、ドライブCの検出後、コントローラープログラムの実行を中断します。 デバッグウィンドウで、一部のデータがキャッチされたことがわかります。多くのデータがあります。

その後、次のように行きました-デバッグウィンドウからバッファーの内容をMS Exelにコピーして列に分割し、変数名を含む最初の列を削除し、その後、値を持つ列を新しいテキストファイルにコピーし、次のようなものを取得しました:

58453 54527 42069 38143 42069 38143 ...

ここで、便利な言語で結果を処理するプログラムを作成します。これにはC#を使用しました。 各入力uintをデータ、アドレス、およびアクセスモードに分割し、読みやすいレポートを作成する必要があります。 これは、たとえば次のように、通常のビットシフトとビット単位の操作で非常に簡単に実行されます。

var busData = uint.Parse(entry); uint data = (busData & 0xFF); uint address = ((busData & 0xFF00) >> 8); uint rw = (address & 0x30)>>4; address = (address & 0x0F);

しかし、プログラムを実行すると、大きな問題が発生しました。ファイルの多くのレコードにアクセスモード11が含まれていたため、読み取り/書き込み信号がありませんでした。 インターラップへの入り口はこれらの信号の1つでのみ可能であるため、インターラップはバスサイクルよりも長く続き、有効なデータを読み取る時間がありません。

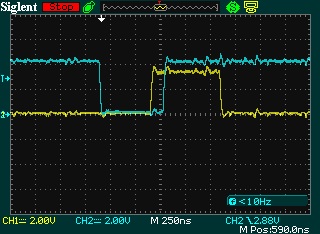

この仮説をテストするために、割り込みの入り口でピンGPIOB.2を1に設定し、出口でそれを0にリセットし、その後オシロスコーププローブを掛けることにしました。

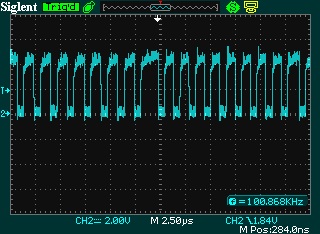

結果は憂鬱でした:

ご覧のように、入力用に12クロックサイクルが約束されているにもかかわらず、システムはI / Oサイクルの最後にインターラップに入ります。 (裸の)属性でさえ助けにはなりませんでしたが、その違いはまったく重要ではありませんでした。

これは気分を害しましたが、コントローラーのオーバークロックを試みることにしました-同じAVRはオーバークロックに非常に優れていたので、STM32がこれでどのように動作しているかを確認してください。 これを行うには、 system_stm32f10x.cファイルに移動して、システムクロックSetSysClockTo72を初期化する手順に進み 、次の行を見つける必要があります。

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

この行では、定数RCC_CFGR_PLLMULL9をさらに変更する必要があります。 私はすぐに言います-私はすべてのオプションを試し、最終的に最大値RCC_CFGR_PLLMULL16に落ち着きました 。 したがって、コントローラーは、浴することなく、72ではなく128 MHzの周波数で完全に巻き上げられました。

ちなみに、同期して動作させるために、ISAクロックにコントローラークロック信号を接続することは非常に良いことですが、デバッグボードに水晶をはんだ付けしたくなかったので、これはしませんでした。

オシロスコープの出力を見てみましょう。

最後に、インターラプトを処理する時間があるのに十分早く入力し始めました! もう一度入力して、分析してみましょう。

レポートにアクセスしているレジスタの名前がすぐにフォーマットされるように、プログラムにいくつか追加しました。 誤ったアクセスモードの場合、無効なデータに関する行がレポートに追加されます。

プログラムの結果は次のとおりです。

WRITE: Cylinder Low [0x1F4] VALUE: 0x55 READ: Cylinder Low [0x1F4] VALUE: 0x55 WRITE: Cylinder Low [0x1F4] VALUE: 0xAA READ: Cylinder Low [0x1F4] VALUE: 0xAA WRITE: Cylinder Low [0x1F4] VALUE: 0x0F READ: Cylinder Low [0x1F4] VALUE: 0x0F WRITE: Cylinder Low [0x1F4] VALUE: 0x00 READ: Cylinder Low [0x1F4] VALUE: 0x00 READ: Status [0x1F7] VALUE: 0x50 WRITE: Drive/Head [0x1F6] VALUE: 0xA0 READ: Status [0x1F7] VALUE: 0x50 WRITE: Drive/Head [0x1F6] VALUE: 0x04 WRITE: Drive/Head [0x1F6] VALUE: 0x00 READ: Status [0x1F7] VALUE: 0x50 WRITE: Drive/Head [0x1F6] VALUE: 0xA0 READ: Status [0x1F7] VALUE: 0x50 WRITE: Drive/Head [0x1F6] VALUE: 0xA0 READ: Status [0x1F7] VALUE: 0x50 WRITE: Command [0x1F7] VALUE: 0x10 READ: Status [0x1F7] VALUE: 0x50 READ: Status [0x1F7] VALUE: 0x50 WRITE: Drive/Head [0x1F6] VALUE: 0xA0 READ: Status [0x1F7] VALUE: 0x50 WRITE: Drive/Head [0x1F6] VALUE: 0xA0 READ: Status [0x1F7] VALUE: 0x50 WRITE: Command [0x1F7] VALUE: 0xEC READ: Status [0x1F7] VALUE: 0x58 READ: Data [0x1F0] VALUE: 0x5A READ: Data [0x1F0] VALUE: 0xFF READ: Data [0x1F0] VALUE: 0x00 READ: Data [0x1F0] VALUE: 0x10 READ: Data [0x1F0] VALUE: 0x00 READ: Data [0x1F0] VALUE: 0x00 READ: Data [0x1F0] VALUE: 0x3F READ: Data [0x1F0] VALUE: 0x00 READ: Data [0x1F0] VALUE: 0x00 READ: Data [0x1F0] VALUE: 0x00 READ: Data [0x1F0] VALUE: 0x45 ...

ご覧のとおり、無効なデータはもうありません。

BIOSが検出を実行する方法を理解してみましょう。

最初は、アドレスを指定するレジスタに常に書き込みと読み取りを行い、書き込まれた値と同じ値が確実に読み取られるようにします。 ATAコントローラがシステムにない場合、BIOSはこのレジスタ0x1F4を長時間読み書きしようとします-これは、コントローラボードが引き出されたレポートの例です。

WRITE: Cylinder Low [0x1F4] VALUE: 0x55 READ: Cylinder Low [0x1F4] VALUE: 0xFF WRITE: Cylinder Low [0x1F4] VALUE: 0x55 READ: Cylinder Low [0x1F4] VALUE: 0xFF ... WRITE: Cylinder Low [0x1F4] VALUE: 0x55 READ: Cylinder Low [0x1F4] VALUE: 0xFF WRITE: Cylinder Low [0x1F4] VALUE: 0x55

次に、 0x10コマンドを送信します。この値はmark_ablovによって親切にプロンプトされ、ディスクを強制的に磁気ヘッドをセクター0に再配置する古い再調整コマンドです。その後、BIOSはステータスバイトをチェックし、コマンドの完了を待機します(ハードドライブがBUSY状態に入らないこともわかります) 、すぐに彼が完了したと応答します)

そして最後に-コマンド0xEC 、 DRIVE IDENTIFY 、それに応答して、ハードは256個の16ビットワードのディスク情報を提供します。

ポート0x1F0から読み取りを開始する前に、BIOSはレジスタ0x1F7からステータスバイトを要求し、ディスクの準備が整うのを待ちます。

ここで、残念ながら、私は自分の間違いに気付きました。制御レジスタは8ビットであるため、データは8ビットで出力されることにしました。 しかし、判明したように、データは16ビットで出力されるため、256バイトの下位バイトしか受信しませんでした。 完全な情報を取得するには、スキームを少しやり直してGPIOD全体をデータに渡し 、アドレスとアクセスモードを他のピンに表示する必要があります。もちろん、それらの処理の遅延が増加します。

したがって、現時点では停止しましたが、近い将来、モニターとしてではなく、デバイスとしてバスに座って作業を続けます。 ISAバスには素晴らしいIOCHRDY信号があり、デバイスがIOサイクルの期間を増やす必要があることを知らせる非アクティブレベルを設定します。これは、ピンを出力に切り替えてステータスを発行するのに十分な時間があることを意味します。

これですべてです。見てくれてありがとう。

更新 :

興味深いものを発見しました。 プロジェクト設定でO3の代わりに最適化O1を設定した場合、インターラップを入力する時間はまさにそのとおりです。 いくつかの調査の後、O2またはO3最適化をオンにすると、コンパイラーが命令を再配置することがわかりました。そのため、信号ピンはインターラップに入った直後ではなく、コードの一部が実行された後に1に設定されます。

したがって、オシロスコープでO1を最適化すると、システムが割り込みプロセッサに早く入りましたが、このプロセッサの実行時間はO3の場合よりも長いことがわかります。