誰も気にしない、猫の下で歓迎。

したがって、ファームウェアの作成はいくつかの段階に分けることができます。

1.受け取りたいものを決定し、紙に、頭の中に、またはVisioに、将来のデバイスの構造図を描きます。 私の場合、これはALUで、入力があります:各4ビットの2つのオペランド、リセット入力、同期入力、2ビットのオペレーションコード入力(00-加算、01-減算、10-乗算、11-結果は0)で終了します8桁の結果。

2.プロジェクトが複雑な場合は、C#などの高レベル言語でビヘイビアモデルを記述する必要があります。これにより、動作方法を理解できます。この場合、CまたはC#モデルで記述するため、この項目はスキップします。このデバイスは多くの機能を備えており、私よりも優れていると確信しています。

3.実際にコードを記述します。このため、System Verilogを強調する構文でNPPを使用しますが、任意のテキストエディターまたはマイクロサーキットのモデリング、合成、トレース用のプログラムのいずれかで記述できます。

この段階でのファームウェアコードは論理モデルと呼びますが、ソースが異なる場合があります。

4.論理モデルのテストを作成していますが、これにはいくつかの方法を使用できます。 また、この段階では、テストとモデルを組み合わせます。

5.シミュレーション環境でテストを行ってモデルを実行します。 モデリングにはQuestaSimを使用しています。これはMentor GraphicsのModelSimの高度なバージョンです。

6.テストが成功した場合、合成に進むことができます。 合成には、Mentor GraphicsのPrecision Synthesisを使用します。 ただし、チップの製造元を提供するソフトウェアを使用できます。 合成の結果、* .edfおよびVerilog形式のファイルを取得します。これは、FPGA内のブロックからCAD合成によって組み立てられた論理モデルであり、それらの間の関係の記述です。 これらのファイルをネットシートと呼びます。

7.論理モデルの代わりにVerilog形式のシートなしファイルを接続し、シミュレーションを再実行して、合成が成功し、シンセサイザーが余分なものをスローしないようにする必要があります。 また、この段階では、論理モデルの受信ネットリストの適合性をチェックする正式な検証手段を使用できます。

8.ネットリストがテストに合格したら、FPGAでネットリストの配置とトレースを開始できます。このため、アクテルLibero IDEの一部であるアクテルデザイナーを使用します。 この段階で、完成したFPGAファームウェアと、同様に重要なことに、回路の修正されたネットリストと時間遅延を取得します。ネットリストは再びVerilog形式になり、遅延は* .sdf形式で生成されます。

9.ここで、時間遅延を伴うトレースの結果として取得されたネットリストをシミュレートし、すべてが機能することを確認する必要があります。

10.すべてが実際に機能する場合は、フラッシュできます。

ALUに戻ります。

SystemVerilogのコードは、少なくともハードウェア記述に関する部分でモジュールで構成されています。 テスト時には、クラスとプログラムのキーワードが表示されます。

悲しいことではありませんが、SystemVerilogまたは少なくともVerilogのタグはありませんが、VHDLのタグはあります。

ALUモジュールを部分的に分析しましょう。

最初に、モジュールの名前と入力/出力を発表します。最初の段階で定義したことを忘れないでください。

module ALU ( input rst, clk, // input [1:0] cmd, // input [3:0] a,b, // output logic [7:0] res // );

次に、組み合わせ部分とトリガー部分を接続するためのいくつかの内部ラインを宣言します。

logic [3:0] A, B; logic [1:0] Cmd; logic [7:0] outpRes;

ここで、しばしばALUの組み合わせまたは非同期について説明します。

always_comb begin unique case(Cmd) 2'b00: begin:add outpRes = A+B; end:add 2'b01: begin:sub outpRes = AB; end:sub 2'b10: begin:mul outpRes = A*B; end:mul 2'b11: begin:div outpRes = 0; end:div endcase end

そして最後に、ALUは私たちと同期するため、トリガーまたはALUの同期部分

always_ff @(posedge clk, posedge rst) if (rst) begin res <= '0; A <='0; B <='0; Cmd <='0; end else begin A[3:0] <= a; B[3:0] <= b; Cmd <=cmd; res <= outpRes; end

キーワードでモジュールを閉じます:

endmodule

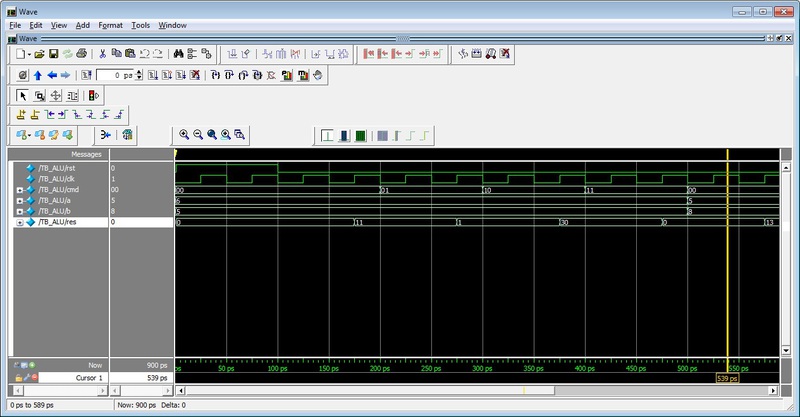

次に、テストを作成してシミュレーションを実行し、次のタイミング図を取得します。

操作が実行されていることがわかりますが、入力と出力で2クロックサイクルの遅延があるため、これを修正できますが、Core i7を作成するのではなく、例を見てみましょう。それでは、そのままにして、合成に進みましょう。

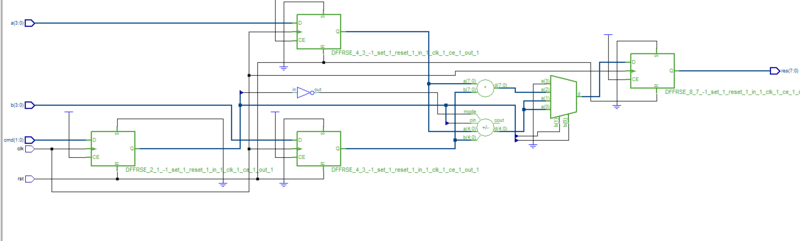

シンセサイザーは、私たちの回路が上の図のようになることを決定しました。実際、ここで私は彼に同意しますが、これは常にそうではありませんので、もう一度テストを実行することさえせず、すぐにクリスタルへのトレースを開始します。

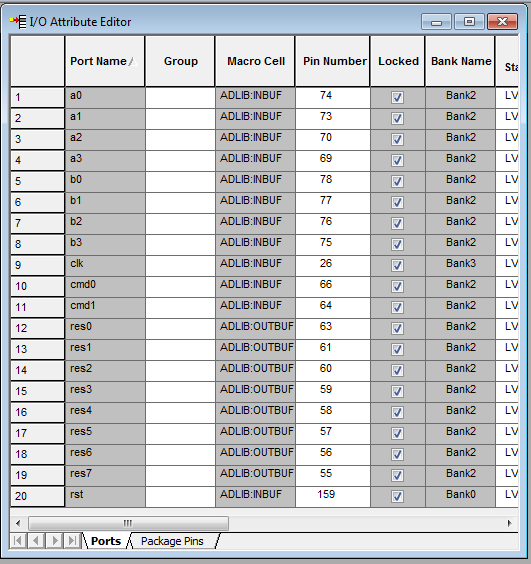

なぜなら キットデザインがあるので、FPGAの結論を次のように整理します。

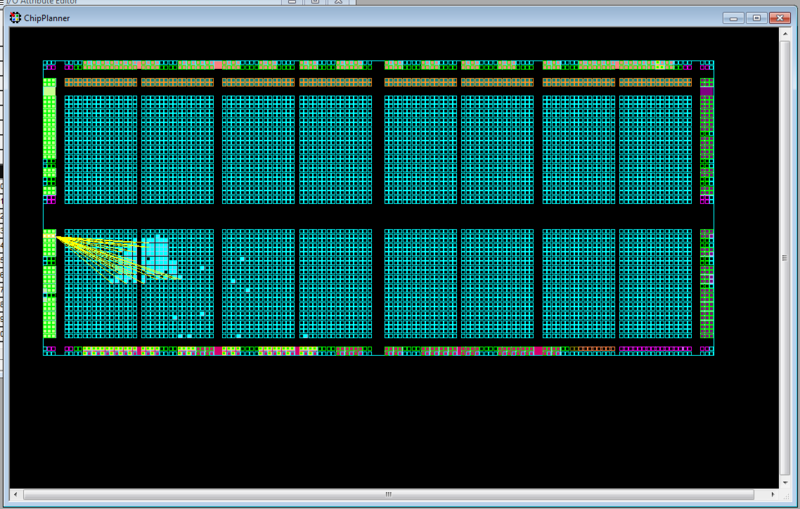

ちなみに、下の図のトレーサーの結果(結晶内の要素の配置)は、この段階で、結晶に沿って要素を移動できます。

黄色はクロック回路を示します。

これで私は私の話を終わらせたいと思います、ビデオは後であります。

最後まで読んでくれた皆さんのおかげで、私はテキストのスタイルと考えられる誤りをおaびしますが、私は作家ではなく、ただ学習しています。

PS 3年前からFPGAに興味を持っていたこのALUプロジェクトは1時間で完了しました。障害を導入するための1つの手法をテストするには、単純なレイアウトが必要でした。