FPGAで働いていた多くの人は、x86プロセッサ、周辺機器などを搭載して、完全にコンピューターを作るかどうかではないと考えていたと思います。 多くの場合、8ビットコンピューターはFPGAに実装されていましたが、これはPC全体です...

FPGAで働いていた多くの人は、x86プロセッサ、周辺機器などを搭載して、完全にコンピューターを作るかどうかではないと考えていたと思います。 多くの場合、8ビットコンピューターはFPGAに実装されていましたが、これはPC全体です...

正常に動作するには、x86プロセッサに加えて、すべての実装された割り込み(SDカードの「ディスク」へのアクセスを含む)、VGA互換ビデオカードのBIOS、すべての周辺機器、メモリコントローラー、タイマーなどが必要です。 このタスクは一見思われるよりもはるかに複雑ですが、それにもかかわらず、 ZetCPUプロジェクトで解決されました。

制限事項-数学コプロセッサーなしで、12.5Mhzで動作するのは16ビットモードのみです。

鉄

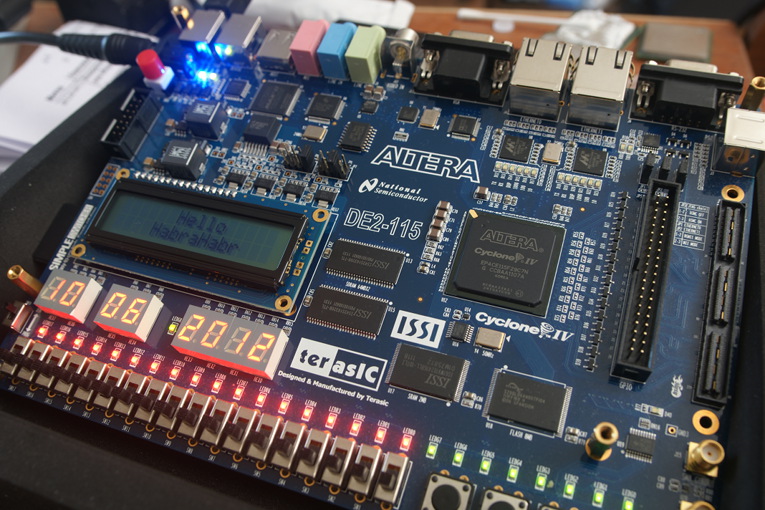

まず、FPGAを備えたデバッグボードが必要です。 Terasic DE2-115ボード ( 115k。LEのアルテラCyclone IV)が本当に気に入りました。 学生の価格は299ドルで、1チップの小売価格よりも低くなっています。

ボードには多くのビルトインアイロンがあります-2 x 8MB SDRAMメモリ、256KB SRAM、1MBフラッシュメモリ、2 PHY 1Gbイーサネット、VGAに接続するためのVideoDAC、LED /スイッチ/ボタン、SDカードスロットなど。 ただし、このプロジェクトですべてが使用されるわけではありません(SDカード、フラッシュ、SDRAM、VideoDACのみ)。

また、プロジェクトは学生価格59ドルでDE0 Nanoで開始できますが、そこではテキストモードのみが機能します。

打ち上げ

インストールには、説明に記載されていない明白でない点がいくつかあります。

- DE2_115_ControlPanel.sofファームウェアをボードにダウンロードします

- DE2 ControlPanelを起動し、指示に従ってBIOSとブートディスケットをフラッシュメモリに入れます

- WinImageではなくwin32-image-writerを使用して、SDカードにハードディスクイメージを書き込みます。大きなカードではブートイメージが破損します。

- BIOS / VGA BIOSをコンパイルするか、インストールアーカイブから既製のものを取得します

- Verilogで書かれたPCカードをQuartusでコンパイルするか、既製のkotku.sofをボードにフラッシュします

これで、モニター、PS / 2キーボードをボードに接続し、電源を入れることができます:-)

プロセッサ、周辺機器に命令を追加し、Verilogソースの命令の実装を確認できます...

整数除算の実装例

module zet_div_uu(clk, ena, z, d, q, s, div0, ovf); // // parameters // parameter z_width = 16; parameter d_width = z_width /2; // // inputs & outputs // input clk; // system clock input ena; // clock enable input [z_width -1:0] z; // divident input [d_width -1:0] d; // divisor output [d_width -1:0] q; // quotient output [d_width -1:0] s; // remainder output div0; output ovf; reg [d_width-1:0] q; reg [d_width-1:0] s; reg div0; reg ovf; // // functions // function [z_width:0] gen_s; input [z_width:0] si; input [z_width:0] di; begin if(si[z_width]) gen_s = {si[z_width-1:0], 1'b0} + di; else gen_s = {si[z_width-1:0], 1'b0} - di; end endfunction function [d_width-1:0] gen_q; input [d_width-1:0] qi; input [z_width:0] si; begin gen_q = {qi[d_width-2:0], ~si[z_width]}; end endfunction function [d_width-1:0] assign_s; input [z_width:0] si; input [z_width:0] di; reg [z_width:0] tmp; begin if(si[z_width]) tmp = si + di; else tmp = si; assign_s = tmp[z_width-1:z_width-d_width]; end endfunction // // variables // reg [d_width-1:0] q_pipe [d_width-1:0]; reg [z_width:0] s_pipe [d_width:0]; reg [z_width:0] d_pipe [d_width:0]; reg [d_width:0] div0_pipe, ovf_pipe; // // perform parameter checks // // synopsys translate_off initial begin if(d_width !== z_width / 2) $display("div.v parameter error (d_width != z_width/2)."); end // synopsys translate_on integer n0, n1, n2, n3; // generate divisor (d) pipe always @(d) d_pipe[0] <= {1'b0, d, {(z_width-d_width){1'b0}} }; always @(posedge clk) if(ena) for(n0=1; n0 <= d_width; n0=n0+1) d_pipe[n0] <= d_pipe[n0-1]; // generate internal remainder pipe always @(z) s_pipe[0] <= z; always @(posedge clk) if(ena) for(n1=1; n1 <= d_width; n1=n1+1) s_pipe[n1] <= gen_s(s_pipe[n1-1], d_pipe[n1-1]); // generate quotient pipe always @(posedge clk) q_pipe[0] <= 0; always @(posedge clk) if(ena) for(n2=1; n2 < d_width; n2=n2+1) q_pipe[n2] <= gen_q(q_pipe[n2-1], s_pipe[n2]); // flags (divide_by_zero, overflow) always @(z or d) begin ovf_pipe[0] <= !(z[z_width-1:d_width] < d); div0_pipe[0] <= ~|d; end always @(posedge clk) if(ena) for(n3=1; n3 <= d_width; n3=n3+1) begin ovf_pipe[n3] <= ovf_pipe[n3-1]; div0_pipe[n3] <= div0_pipe[n3-1]; end // assign outputs always @(posedge clk) if(ena) ovf <= ovf_pipe[d_width]; always @(posedge clk) if(ena) div0 <= div0_pipe[d_width]; always @(posedge clk) if(ena) q <= gen_q(q_pipe[d_width-1], s_pipe[d_width]); always @(posedge clk) if(ena) s <= assign_s(s_pipe[d_width], d_pipe[d_width]); endmodule

テストに合格します

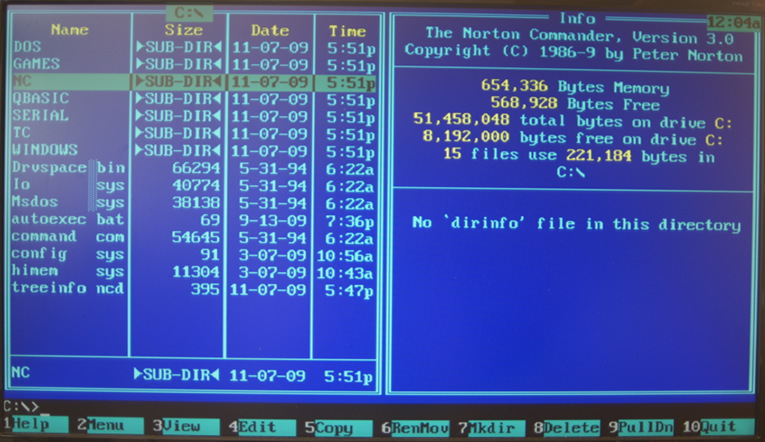

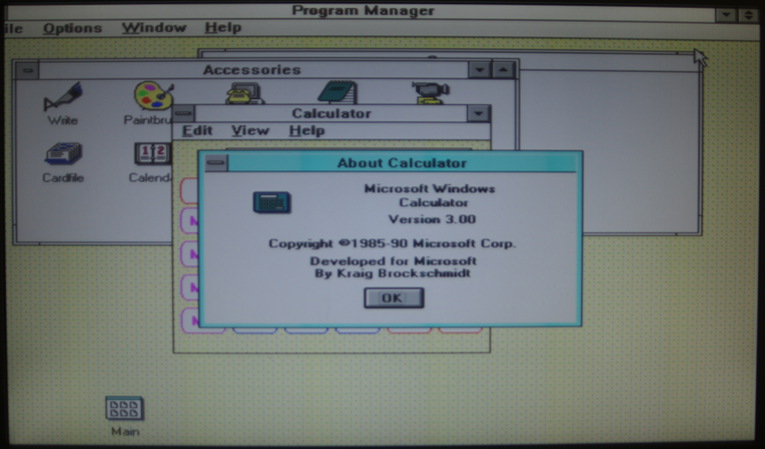

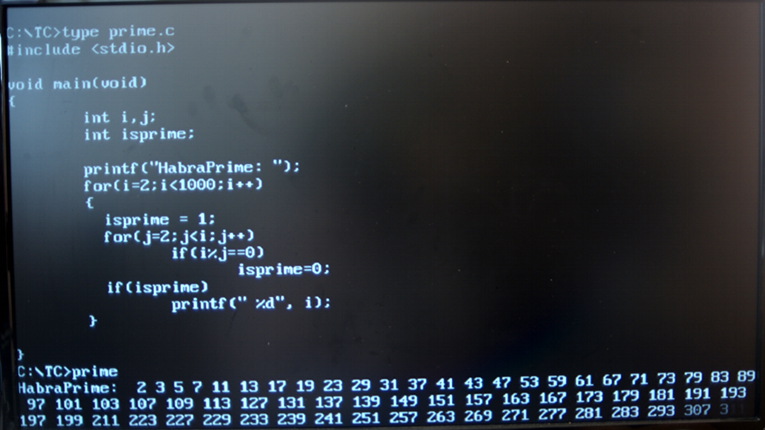

スクリーンコピーについて事前に謝罪します。

次はプログラミングです。 コンパイルと実行の速度は懐かしさを呼び起こします...

おわりに

この記事がFPGAのパワーを信じ、Verilogの研究を続けてくれることを願っています。そして、誰かが自分のPCブラックジャックを作る夢を叶えるかもしれません:-)

質問/コメント?