MITのエンジニアは、ポリマーでコーティングされたシリコン基板上に厚さ15 nmのワイヤを自己組み立てする新しい方法を発明しました。 15 nmの厚さは、最新の最小チップのコンポーネントのサイズの2倍以上小さくなっています。 したがって、マイクロ回路のさらなる小型化への道が開かれます。

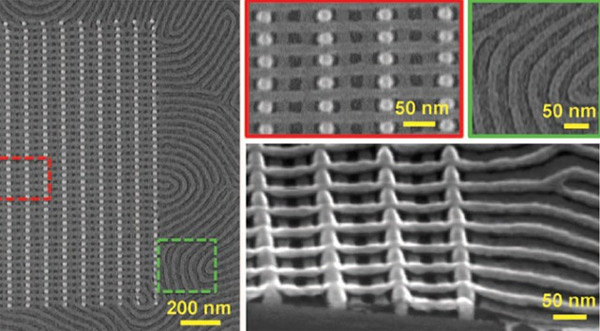

他の実験では15 nmのワイヤが得られましたが、MITのエンジニアが複数の層(2つ)で3D構造を設計することができたのは初めてでした。

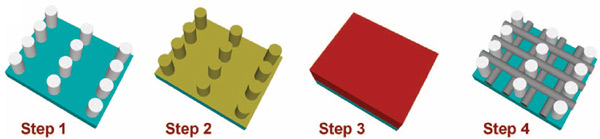

ワイヤの自己組み立ての段階的なプロセスを図とビデオに示します。 シリコン基板上に、厚さ10 nmの小型カラムのグリッドが電子リソグラフィーによって作成されます。 これは、Intel、TSMC、および他の企業の工場に設置されている電子リソグラフィ用のシリアル機器でも実行できます。

それらは、ブロック共重合体でコーティングされており、その特性上、長い円筒構造にカールする傾向があります。 カラム間の距離を正確に計算することにより、ブロック共重合体を事前に「プログラム」して、必要な形状と太さのワイヤを作成し、マイクロ回路の表面に沿って配線することができます。 列は、1つではなく2つのワイヤ層のプロパティを設定します。これにより、複雑な3D構成を作成できます。 将来的には、各層の構造を完全に制御しながら、3層構成に切り替えることができます。

これは、サブミクロンの電子回路を作成するための非常に重要な技術です。 MITの研究者は、1年以内に最初の実行可能な電子デバイスを作成するつもりだと言います。