テキストの形式は、相手に対する冗談と批判です。

この投稿はこのRNGの開発者にとって興味深いものではないと思います(彼らはすでに賞を受賞しています)が、他の誰かにとっては、一般的な開発にとってはおそらく興味深いでしょう。

RNGはIntelから何について沈黙していますか? そして、彼は多くのことについて沈黙していますが、最初に用語を決定する必要があります。

Random Number Generator(RNG)には共通名があります。 それらは、PRNG(疑似乱数ジェネレーター)とTRNG-True RNGに分かれています。 暗号IPを発行する各自尊心のあるオフィスは、その武器庫にTrue RNGを保有する義務があります。

さらに良いのは、True RNGがコンパクト、高速、そして最も重要な場合-デジタル(エキゾチックな動物のショットキーダイオード、ノイズの多い抵抗器などのアナログのトラブルがなく、「維持」が難しいためです)。

つまり、暗号化の真のエントロピーも必要であるため、True RNGなしには方法がありません。

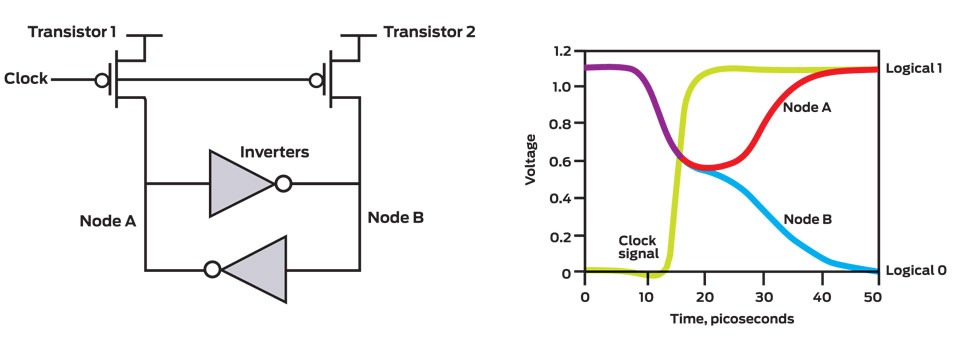

True RNGに興味がある人は、 最初のIntel RNGが最初に説明された資料に注意する必要があります。

それらは、エントロピーのソースとして、そこにある一対の発振器と組み合わせて「ノイズ抵抗器」を使用します。 これはIntelからの最初のTrue RNGであり、最近まで(Ivy Bridge製品のリリース前)しかありませんでした。 原則として、最初のIntel True RNGは正しく機能しましたが(スマートではありませんでしたが)、移植性(生産技術間)(個人的な仮定)にアレルギーがあり、特別な栄養が必要でした。 制限。 そのため、チップセットの背面に「保持」されていましたが、さまざまな理由で、プロセッサから1年または2年遅れていました(生産技術により)。

Intelはこのマゾヒズムを止めることを決定し、2008年に2つの開発グループに新しいTrue RNGを作成するタスクを与えました。 デジタルであるために、はい、早く、そして私は無駄に貴重なエネルギーを食べないように、しかし、私はさまざまな認証に合格しました。

開発の過程で、このテーマに関する2つの出版物がありましたが、それらについて詳しく説明する必要があります。 残念ながら、それらはパブリックドメイン(IEEEのみ)にはありませんが、シーカーは常に見つけます。

まず、 「45nm CMOSの4Gbps 0.57pJ /ビットプロセス電圧温度変動耐性全デジタル真乱数ジェネレーター」

タイトルや要約から資料まで、Intelは冗談を言うのが好きではないことがすぐに明らかになり、名前を尋ねることなく「みんなを引き裂く」。 しかし、最後まで読んだとき、私は長い間笑いました。 笑いのハイライト:

- 私たちはすべてNIST STSテストスイートでテストを行っており、RNGはすべてのテストに合格しています。

さて、大丈夫、最初のテストは常にシミュレーションであり、あなたはこれらに同意することができますが、という事実に同意することはできません

- 開発者によると、エントロピーのソースは完全にデジタルです。

原則として、エントロピーのソースの中心要素は双安定セルであり、これは本質的にデジタルです

、しかし、それが提出された方法は、すでに全デジタルの範囲を超えています。

、しかし、それが提出された方法は、すでに全デジタルの範囲を超えています。

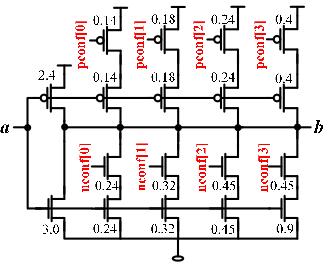

使用済みのインバーター(合計2)の例を次に示します。これには、電源とグランド用に特別に選択された8つのタップがあります。

それらのオン/オフを切り替えると、インバータのスイッチングレベルを調整できます(実際のチップでは、トランジスタはすべて異なります)。 開発者の目標は単純でした-双安定素子で使用されるインバータのペアを同じレベルで切り替えることです。 彼らはおそらく目標を達成しました(技術の普及は補償されました)が、この古代のソリューション(私よりも古い)と呼ばれるのは-すべてデジタル-それは単なる冒aspです、私見です。

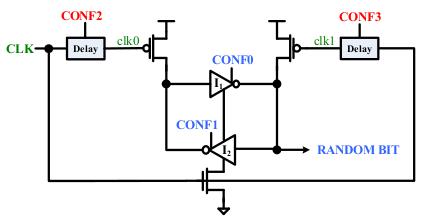

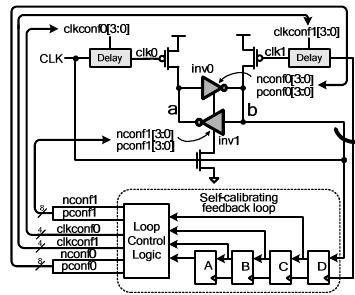

設計のための標準デジタルライブラリでは明らかに利用できない「特殊デジタルインバーター」に加えて、インテルの研究者は、接続の寄生容量(遅延要素)を補償するための別の全デジタルソリューションを追加しました。補償。 その結果、私たちはそのような「オールデジタル」を得ました

ここで、CONF0-1はインバータのスイッチングレベルを調整するための8ビットレジスタであり、CONF2-3は幹線の浮遊容量(遅延設定)を補償するための4ビットレジスタです。 一般に、CONF0-3はシステムのバランスをとるために使用されます。これがないと幸運です(チップはチップとは異なります):ノイズがインバータースイッチングの差よりも小さい場合は動作しません。 、可能かつ実用的なオプションですが(すべてガウスによる)。

まだ文句を言う(技術のばらつきをシミュレートする方法、統計テストに合格した結果を評価する方法、「低エネルギー」ソリューションについてなど)がありますが、2番目の出版物に行く方が良いでしょう。

2番目の「2.4GHz 7mW全デジタルPVT-Variation Tolerant True Random Number Generator in 45nm CMOS」は 、すべての主要ポイントについて最初の繰り返しを行い、「論争の的となる評価のポイント」を追加し、4 Gbit / sから2.4Gbps

- 同じ下位の統計検定、エントロピーのソースなど。

- 自己較正メカニズムが追加されました。これについては、より詳細に検討する必要があります。

自己校正システムは次のように動作します。システムは生成されたビットをチェックし、その値に応じて、エントロピーのソースを再構築して、次回に逆の値を受け取ります。 たとえば、現在の(生成された)値が「0」の場合、エントロピーのソース(インバータ部品と接続線の負荷の新しい組み合わせを使用)は逆方向に「微調整」され、より高い確率で「1」が生成されます。

はい、上記の例は非常に単純化されています。開発者によると、自己キャリブレーションシステムは決定時に1、2、および4の連続ビットを評価するためです(詳細は記載されていません) 合計すると、このソリューションによって出力で均一性(タイプ '1'および '0'の値の均一な分布)が得られることに同意できますが、予測不能性と独立性はどうですか? しかし、Jesse Walker氏でさえ、乱数ジェネレーターの予測不能性と独立性などの重要なパラメーターに言及しました。

別の妥当な質問がテストで発生します-テストされる期間とサンプルの数は?

その結果、5つのテスト(周波数、ブロック周波数、実行、累積合計、FFT)を含む表がありますが、パッケージには15があります。最初の記事でアナログシミュレーションからデータを受け取った場合、2番目で、ハードウェア(製造済み)であり、これにより、下位チェックの合理的な理由はないはずです(ある意味-生成が困難です)。

この科学的なキャンペーンは終了し、広告のみがほとんど残っていました。

IDF 2011で、Ivy BridgeのRNGは何気なく発表されましたが、このトピックに関するIEEE Spectrumの出版物でのみ詳細に説明されています。

この記事の長年にわたるHabréの翻訳では、コメントで、エントロピーのソースからのこれらの「ほぼランダムな」データのAESを使用した二重漂白について徹底的に調べました 。

同じ写真(詳細のみ)およびIDF 2012

この記事では、「 2つのインバーターのほとんどランダムな出力を512ビットずつ収集することから始まる」というフレーズに注目したいと思います。 このソリューションの実装を明確に提示することはできませんでした。 まあ。

それは何についてですか?

いずれにせよ、Intelの開発者はうまくやっており、22nmテクノロジーでそのような「デジタルソリューション」をリリースできており、とてもクールです。

PS資料の提示が一部の人々にとって混乱しているように思われる場合、または質問が生じた場合、私は喜んで明確にするか回答します。

PS 2.編集してくれてありがとう