この記事は、 VHDL FPGAプログラミングの初心者およびその方法を学びたい人を対象としています。 以前、PICコントローラーに実装された同様のタスクを含む記事は、Habrで既に検討されていました。 この記事では、FPGAを使用してLEDの輝度を変更する方法について説明します。

この記事は、 VHDL FPGAプログラミングの初心者およびその方法を学びたい人を対象としています。 以前、PICコントローラーに実装された同様のタスクを含む記事は、Habrで既に検討されていました。 この記事では、FPGAを使用してLEDの輝度を変更する方法について説明します。

したがって、作業の目標: PWMの概念を習得し、それをLEDの輝度の変更に適用すること。 実装するには、 Xilinx ISE Project Navigator v12.3開発環境でVHDLプログラミング言語を使用します。

目標の達成に移りましょう

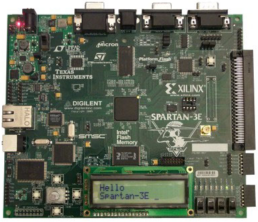

実装には、FPGAを備えたハードウェアが必要です。手元にあるSpartan-3Eスターターキット( DataSheet )を選択しました。 ザイリンクスISE Project Navigatorをインストールする必要もあります(バージョン12.3がインストールされています)。 基本的に、すべてが機能する準備ができています。 電源をボードに接続し、さらにプログラミングするためにUSB経由でコンピューターに接続するためだけに残ります。

パート1. LEDの輝度を変更する理論。

LEDの輝度は、さまざまな値の定電圧を(たとえば、可変抵抗器によって)印加することで調整できます。 しかし、ボードには可変抵抗器のないLEDがあり、値「1」を取り、完全な明るさ、つまり「0」で点灯します。 では、そのような単純なデバイスの明るさをどのように調整するのでしょうか? 答えはPWMです。 全体のポイントは、このLEDを非常に速く「点滅」させて、点滅が目に見えないことですが、薄暗いLEDだけが見えることです。 より正確には、点火中にLEDに過渡現象が発生する、つまり瞬時に点灯しないということです。 これは私たちが使用するもので、非常に短い時間だけユニットを使用するため、LEDが最大の明るさで点灯する時間はありません。

パート2.新しいプロジェクトの作成。

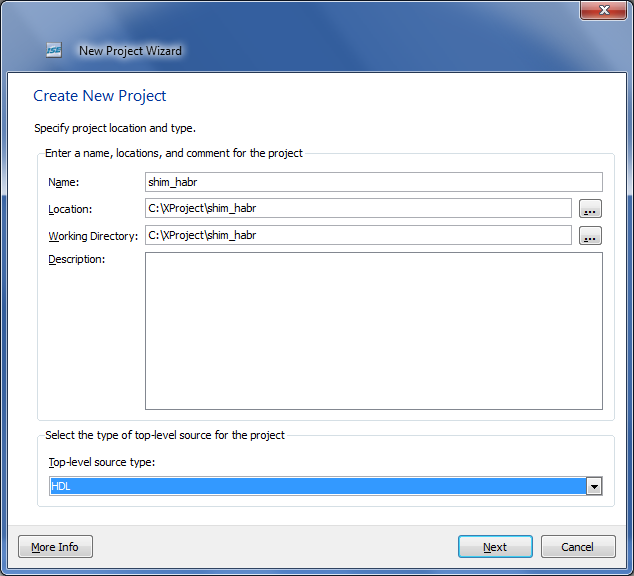

ISE Project Navigatorをダウンロードし、[ファイル]-> [新しいプロジェクト]を選択します。 プロジェクトの名前を書き(shim_habrがあります)、保存するディレクトリを選択し、下から[トップレベルソースタイプ:HDL]を選択します。 次へをクリックします。

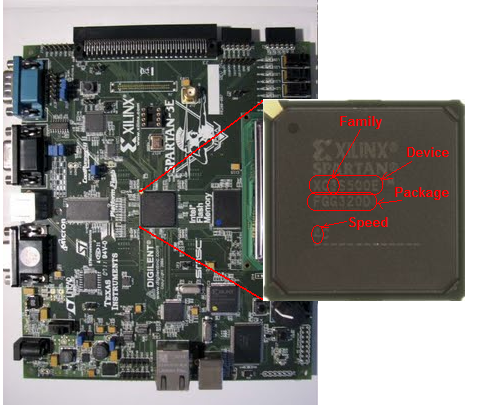

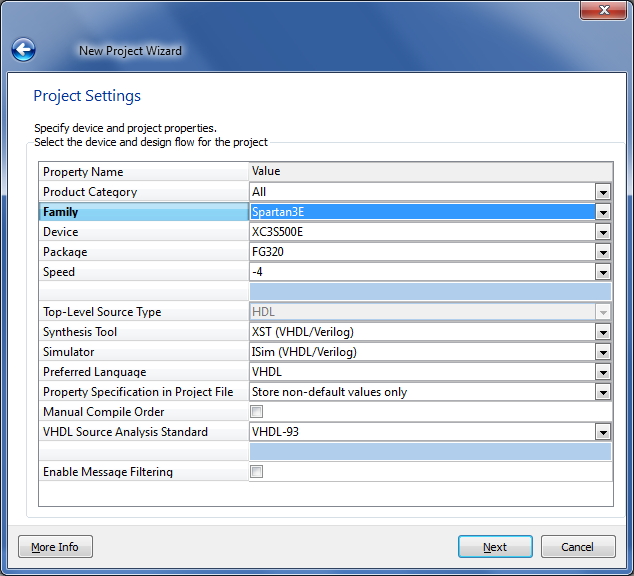

次に、FPGAを選択します。 私の場合、家族:Spartan3E; デバイス:XC3S500E; パッケージ:FG320; 速度:-4。 これらのデータはすべて、チップ自体に表示されるか、データシートで確認できます。

次に、Preferred Language:VHDLを選択し、NextをクリックしてからFinishをクリックします。

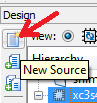

プロジェクトが作成されます。 次に、モジュールを追加する必要があります。ここで、LEDのロジックを説明します。 左上の[新しいソース]ボタンを見つけてクリックします。

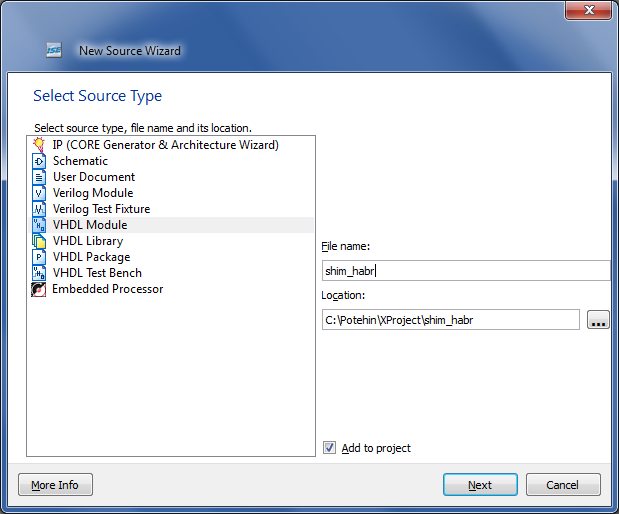

表示されるウィンドウで、VHDLモジュールを選択し、任意のファイル名を書き込みます(shim_habrプロジェクトで名前を付けることができます)。 次へをクリックします。

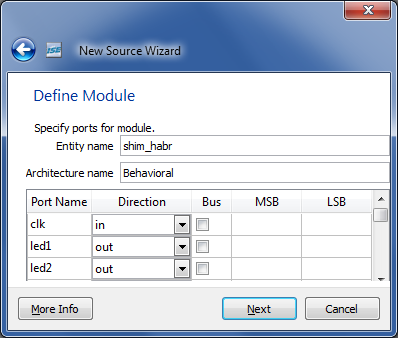

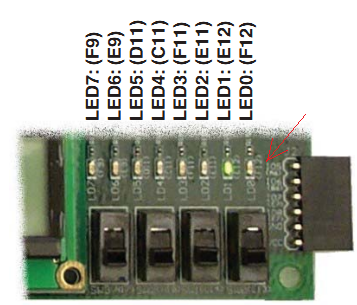

次に、プロジェクトで使用する脚を設定する必要があります。 今これを実行してこのステップをスキップしてから、すべてを手で書くことはできません。 しかし、プロジェクトには3本の足しか必要ないため、ここに足を入れました。 そのため、FPGAに接続された50 MHzボードに取り付けられたクォーツからC9という名前の脚までの基準周波数が必要です。また、ボードに既に取り付けられている2つのLEDも使用します。 これらがE12およびF12という名前でFPGAレッグに接続された2つの右側のLEDであるとします。 クォーツレッグclkを呼び出し、方向:INを設定します 周波数を読み取ります。LEDのある脚はled1とled2であり、値はDirection:OUTです。 それらを管理します。

[次へ]、[完了]の順にクリックします。 プロジェクトのI / Oポートがすでに入力された、開いたテキストエディターが表示されます。

エンティティ shim_habr は

ポート ( clk : STD_LOGIC ;

led1 : STD_LOGICから ;

led2 : STD_LOGICから )

shim_habrを終了します。

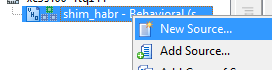

前に言ったように、前の手順をスキップして、すべて手動で入力できます。 次に、ポート名をFPGAレッグの名前にマップする必要があります。 階層内のファイル名shim_habr.vhdを右クリックし、[新しいソース]を選択します。

開いたウィンドウで、Implementation Constrains Fileを選択し、このピンファイルを呼び出します。 [次へ]、[完了]の順にクリックします。

開いた空のファイルに、次のように記述します。

NET "clk" LOC = "C9" ;

NET "led1" LOC = "F12" ;

NET "led2" LOC = "E12" ;

保存します。

データシートで脚の番号を見ることができます。または、この場合、検索を簡素化しました。必要な周辺機器の隣のボードで直接番号を見ることができます。

パート3. LEDの一定の輝度のプログラミング。

shim_habr.vhdファイルに切り替えて、コードを記述します。

アーキテクチャ shim_habrの動作は

定数 clk_freq : integer := 50 _000_000 ; -クォーツ周波数

定数 shim_freq : integer := 10 _000 ; -PWM周波数

定数 max_count : 整数 := clk_freq / shim_freq ; -PWM容量

シグナル数: 整数 範囲 0 から max_count := 0 ; -分周器カウンター

定数 porog : integer := max_count / 48 ; -論理ユニットのパルス幅

始める

プロセス ( clk )

始める

rising_edge ( clk )の 場合

count = max_countの場合

カウント<= 0 ;

他に

カウント<=カウント+ 1 ;

終了する 場合 ;

終了する 場合 ;

終了 プロセス 。

カウント< porog else ' 0 'の場合、 led1 <= ' 1 ' 。

led2 <= ' 1 ' ;

ビヘイビア;

次に、このコードが何をするのか見てみましょう。 まず、行led2 <= '1'に注意してください。 2番目のLEDを最大輝度で点灯させ、そこに論理ユニットを提供します。そのため、最初のLEDのグローの輝度と比較するものがあります。 次に、宣言されたレジスタと定数を確認します。 clk_freq定数は、クォーツの周波数をヘルツで保存します。 shim_freqは、ヘルツ単位のPWMの周波数です。 したがって、必要なPWM周期を取得するには、クロック周波数をPWM周波数で除算する必要があり、PWM周期に対応するメインクォーツのクロックサイクル数を取得します。 本質的に、これはPWMの幅になります。 除算の結果は、定数max_countに書き込まれます。 次に、カウンターカウントを作成します。これは、50 MHzの周波数で0からmax_countまで循環します。 プロセスプロセス(clk)を作成します。 rising_edge(clk)がクォーツからの次の「ティック」を待つ場合の条件は、発生した場合、ユニットにカウントを追加し、最大値までカウントしたかどうかを確認します。 次に、プロセスの外で、次の行を書きます。

カウント< porog else ' 0 'の場合、 led1 <= ' 1 ' 。

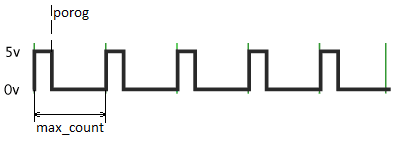

つまり、カウンターがいくつかのしきい値porog値(私にとっては期間全体の1/48、定数の宣言を参照)より小さい場合、論理ユニットはLEDでハングし、LEDの残りの期間は論理ゼロをハングします。 これは図に明確に示されています。

パート4.ファームウェア。

すべての変更を保存し、階層内のshim_habr.vhdファイルを選択し、階層の下からターゲットデバイスの構成プロセスを探して開始します。 プロジェクトがファームウェアファイルに変換されるのを待ちます。その後、iMPACTプログラムウィンドウが開き、FPGAに縫い付けられます。

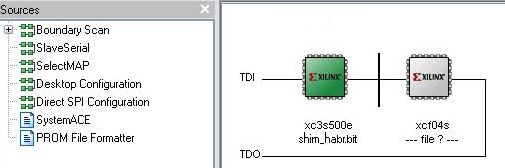

[Boundary Scan]をダブルクリックします。ボードがUSB経由でコンピューターに接続されている場合、次のようなものが表示されます。

xc3s500eのファームウェアファイルを選択するように提案されていない場合は、適切なマイクロサーキットを右クリックして、[構成ファイルの割り当て]メニュー項目を選択します。 ファイル選択ウィンドウで、新しく作成されたshim_habr.bitを選択します。 次に、xc3s500eを右クリックしてから、Programを選択します。 ファームウェアプロセスが開始され、Program Successfulが表示されます。 すべてがそのようになった場合、スカーフを見ることができます=)

パート5. LEDの輝度の滑らかな変化のプログラミング。

したがって、2つのLEDが点灯していることがわかります。1つは明るく、もう1つは暗いです。 それでは、明るさを滑らかに変えてみましょう。 これを行うには、porogを定数ではなく変数にし、最小から最大にスムーズに変更する必要があります。

シグナル porog : 整数 範囲 0 から max_count := 0 ;

しきい値の変化率を設定するには、再びクロック周波数を分周し、より小さい周波数を取得する必要があります。 たとえば、しきい値を1/600秒ごとに1ずつ増やしたいとします。 カウンターを作成します。

定数 max_count_div : 整数 := clk_freq / 600 ;

シグナル count_div : 整数 範囲 0 から max_count_div := 0 ;

また、次の「tick」の場合にプロセス(clk)に追加する場合、rising_edge(clk)の場合は別の条件:

count_div = max_count_divの場合

count_div <= 0 ;

-ここでは、頻度は600に分割されます。

他に

count_div <= count_div + 1 ;

終了する 場合 ;

ここで、頻度を600で割った場所に書き込み、しきい値を1増やし、値が最大に達したら0にリセットする必要があります。

porog = max_countの場合

porog <= 0 ;

他に

porog <= porog + 1 ;

終了する 場合 ;

その結果、全体像は次のようになります。

アーキテクチャ shim_habrの動作は

定数 clk_freq : integer := 50 _000_000 ; -クォーツ周波数

定数 shim_freq : integer := 10 _000 ; -PWM周波数

定数 max_count : 整数 := clk_freq / shim_freq ; -PWM容量

シグナル数: 整数 範囲 0 から max_count := 0 ; -分周器カウンター

シグナル porog : 整数 範囲 0 から max_count := 0 ; -論理ユニットのパルス幅

定数 max_count_div : 整数 := clk_freq / 600 ;

シグナル count_div : 整数 範囲 0 から max_count_div := 0 ;

始める

プロセス ( clk )

始める

rising_edge ( clk )の 場合

count = max_countの場合

カウント<= 0 ;

他に

カウント<=カウント+ 1 ;

終了する 場合 ;

count_div = max_count_divの場合

count_div <= 0 ;

porog = max_countの場合

porog <= 0 ;

他に

porog <= porog + 1 ;

終了する 場合 ;

他に

count_div <= count_div + 1 ;

終了する 場合 ;

終了する 場合 ;

終了 プロセス ;

カウント< porog else ' 0 'の場合、 led1 <= ' 1 ' 。

led2 <= ' 1 ' ;

ビヘイビア;

私たちは放送し、縫い、成功します。 =)ほとんどの場合、LEDは明るく点灯し、サイクルの開始時にのみ暗くなると考えるかもしれません。 カラーミュージックに関する以前の記事でこの効果についてすでに書いた。 事実は、明るさがしきい値に線形ではなく、対数に依存するということです。 つまり、たとえば、1024ビットのPWMを使用して明るさを最小から最大にスムーズに変化させるには、porog変数の次の値を連続して取得する必要があります:0、16、32、64、128、256、512、1024。

宿題。

ご覧のとおり、LEDは徐々に明るさを増していき、ダイヤルされるとすぐに0にリセットされます(実際、書き込みと取得が完了しました)。 ワークアウトとして、滑らかな明るさのセットを作成し、最大の開始点に達すると、滑らかにゼロに減少させることができます。 このタスクに簡単に対処できる人のために、8つの使用可能なLEDの「ランニングライト」を作成することができます。最初のダイオードが点灯して消灯し、2番目のダイオードが点灯します。 うまくいかないが、おもしろい場合は質問してください。答えて説明しようとします。

おわりに

そのため、LEDへのPWMの応用を習得し、FPGAを使用してLEDの輝度を調整することを学びました。 同じ方法を使用して、エンジンの速度、コイルの磁力などを制御できます。

FPGAの習得にご成功をお祈りします!

PS:申し訳ありませんが、仕事でこの記事のプロジェクトのソースを忘れてしまいました...そこから拾い上げたらすぐに投稿します(自宅には何もインストールされていません)。 ただし、彼はここでは本当に必要ではありません。すべてが必要です(できれば、必要です!)。

UPD: 約束されたソース 。