」

」

はじめに

出発点として、アナログからデジタルへの変換を定義します。 アナログからデジタルへの変換は、入力物理量を数値表現に変換するプロセスです。 A / Dコンバーターは、この変換を実行するデバイスです。 正式には、ADCの入力値は、電圧、電流、抵抗、静電容量、パルス繰り返し率、シャフト回転角など、あらゆる物理量にすることができます。 ただし、明確にするために、以下ではADCを排他的に電圧/コードコンバータとして理解します。

アナログからデジタルへの変換の概念は、測定の概念と密接に関連しています。 測定とは、測定された量を特定の標準と比較するプロセスを意味します。アナログ-デジタル変換では、入力量が特定の基準量と比較されます(原則として、基準電圧と)。 したがって、アナログからデジタルへの変換は、入力信号の値の測定と見なすことができ、測定誤差などの計測のすべての概念が適用できます。

ADCの主な機能

ADCには多くの特性があり、その主なものは変換周波数とビット深度と呼ばれます。 変換頻度は通常、1秒あたりのサンプル数(1秒あたりのサンプル数、SPS)、ビット数で表されます。 最新のADCは、最大24ビットの解像度と最大GSPS単位の変換速度を備えています(もちろん、同時ではありません)。 速度とビット深度が高いほど、必要な特性を取得するのが難しくなり、コンバーターがより高価で複雑になります。 変換速度とビット深度は特定の方法で相互に関連しており、速度を犠牲にすることで変換の実効ビット深度を増やすことができます。

ADCタイプ

ADCには多くの種類がありますが、この記事のフレームワークでは、次の種類のみを考慮するように制限しています。

- ADCパラレル変換(直接変換、フラッシュADC)

- シーケンシャルADC(SAR ADC)

- デルタシグマADC(電荷平衡型ADC)

(一般に)異なるアーキテクチャを持つ複数のADCで構成されるパイプライン型および結合型など、他の種類のADCもあります。 ただし、上記のADCアーキテクチャは、各アーキテクチャが一般的な速度ビット範囲で特定のニッチを占有しているという事実のため、最も示唆的です。

直接(並列)変換のADCは、最高の速度と最低のビット深度を備えています。 たとえば、Texas Instruments TLC5540パラレル変換ADCには、わずか8ビットの40MSPSがあります。 このタイプのADCの変換速度は最大1 GSPSです。 ここでは、パイプラインADCはさらに高速ですが、速度の遅い複数のADCの組み合わせであり、この記事の範囲外であることに注意してください。

一連のビットレートの平均的なニッチは、逐次近似のADCによって占有されます。 典型的な値は、100KSPS-1MSPSの変換レートで12〜18ビットです。

最大の精度は、最大24ビットの容量とSPSユニットからKSPSユニットまでの速度を持つシグマデルタADCによって達成されます。

最近使用された別の種類のADCは、ADCの統合です。 ADCの統合は現在、ほぼ完全に他の種類のADCに置き換えられていますが、古い測定器に見られます。

ダイレクトコンバージョンADC

ダイレクトコンバージョンADCは1960年から1970年にかけて普及し、1980年代に集積回路として生産され始めました。 多くの場合、「パイプライン」ADCの一部として使用され(この記事では考慮されていません)、最大1 GSPSの速度で6〜8ビットの分解能を備えています。

直接変換ADCのアーキテクチャを図に示します。 1

図 1. ADC直接変換のブロック図

ADCの動作原理は非常に単純です。入力信号は、コンパレータのすべての「プラス」入力に同時に送信され、「マイナス」信号には、抵抗Rを分割して基準電圧から得られる一連の電圧が供給されます。 1このシリーズは次のようになります:(1 / 16、3 / 16、5 / 16、7 / 16、9 / 16、11 / 16、13 / 16)Uref、ここでUrefはADC基準電圧です。

1/2 Urefに等しい電圧をADC入力に印加します。 その後、最初の4つのコンパレーターが動作し(下から数える場合)、出力に論理ユニットが表示されます。 プライオリティエンコーダーは、出力レジスターによって修正されるユニットの「列」からバイナリコードを形成します。

このようなコンバータの長所と短所が明らかになりました。 すべてのコンパレータは並行して動作し、回路の遅延時間は、1つのコンパレータの遅延時間にエンコーダの遅延時間を加えたものに等しくなります。 コンパレータとエンコーダは非常に高速にできるため、回路全体が非常に高速になります。

ただし、Nビットを取得するには2 ^ Nのコンパレータが必要です(エンコーダの複雑さも2 ^ Nのように増大します)。 図の回路 1. 8個のコンパレーターが含まれ、3ビットあります。8ビットを得るには256個のコンパレーターが必要で、10ビットには1024個のコンパレーターが必要です。24ビットADCには1600万以上必要です。しかし、テクノロジーはそのような高さに達していません。

逐次近似ADC

逐次近似ADCは、フィボナッチにまでさかのぼる「重み付け」アルゴリズムを実装しています。 彼の本「Liber Abaci(1202)」では、フィボナッチは「重量の最適なシステムを選択する問題」、つまり、物体の重量を見つけるためにレバースケールで最小数の計量を必要とする一連の重量を見つけることを検討しました。 この問題の解決策は、「バイナリ」の重みセットです。 フィボナッチの問題について詳しくは、たとえばhttp://www.goldenmuseum.com/2015AMT_rus.htmlをご覧ください 。

逐次近似レジスタ(SAR)D / Aコンバーターは、一連の連続的な "重み付け"を実行することで入力信号の大きさを測定します。つまり、入力電圧の大きさを次のように生成される一連の値と比較します:

1.最初のステップで、1 / 2Urefの値がビルトインのD / Aコンバーターの出力に設定されます(以下、信号が区間(0-Uref)にあると仮定します。

2.信号がこの値より大きい場合、残りの間隔の中央にある電圧、つまりこの場合は3 / 4Urefと比較されます。 信号が設定レベル未満の場合、残りの間隔の半分未満で(つまり、1 / 4Urefのレベルで)次の比較が行われます。

3.ステップ2をN回繰り返します。 したがって、N回の比較(「計量」)は結果のNビットを生成します。

図 2. ADC逐次近似のブロック図。

したがって、逐次近似ADCは次のノードで構成されます。

1.コンパレータ。 入力値と「加重」電圧の現在値を比較します(図2の三角形で示されています)。

2. D / Aコンバーター(D / Aコンバーター、DAC)。 入力で受信したデジタルコードに基づいて「加重」電圧値を生成します。

3.逐次近似レジスタ(SAR)。 逐次近似アルゴリズムを実装し、DACの入力に供給されるコードの現在の値を生成します。 その名前で、このADCアーキテクチャはすべて名前が付けられています。

4.サンプリング保存スキーム(サンプル/ホールド、S / H)。 このADCの動作では、入力電圧が変換サイクル全体を通して一定であることが基本的に重要です。 ただし、「実際の」信号は時間とともに変化する傾向があります。 サンプル保存回路は、アナログ信号の現在の値を「記憶」し、デバイスのサイクル全体を通してそれを変更しません。

このデバイスの利点は、変換速度が比較的速いことです。NビットADCの変換時間はNサイクルです。 変換の精度は、内部DACの精度によって制限され、16〜18ビットになります(24ビットADC SAR、たとえばAD7766やAD7767も登場し始めています)。

デルタシグマADC

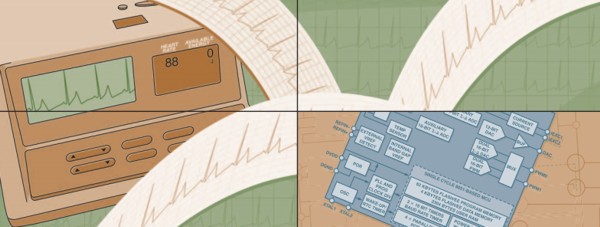

そして最後に、最も興味深いADCのタイプはシグマ-デルタADCであり、文献では電荷平衡ADCと呼ばれることもあります。 シグマ-デルタADCのブロック図を図5に示します。 3。

図3 シグマデルタADCのブロック図。

このADCの動作原理は、他の種類のADCよりもやや複雑です。 その本質は、入力電圧が積分器によって累積された電圧値と比較されることです。 比較の結果に応じて、正または負の極性のパルスが積分器の入力に供給されます。 したがって、このADCはシンプルな追跡システムです。積分器の出力電圧は入力電圧を「監視」します(図4)。 この回路の結果は、コンパレータの出力でゼロと1のストリームになり、デジタルローパスフィルタを通過してNビットの結果になります。 図のローパスフィルター 3.「間引き」と組み合わせて、「間引く」ことによってサンプルの周波数を減らします。

図 4.追跡システムとしてのシグマデルタADC

厳密のために、私は図でそれを言わなければなりません。 図3は、1次シグマデルタADCのブロック図を示している。 2次シグマデルタADCには2つの積分器と2つのフィードバックループがありますが、ここでは考慮しません。 このトピックに興味がある人は[3]を参照できます。

図 図5は、ゼロ入力レベル(上)およびVref / 2レベル(下)のADCの信号を示しています。

図 5.入力でのさまざまな信号レベルでのADCの信号。

シグマデルタADCは、 http : //designtools.analog.com/dt/sdtutorial/sdtutorial.htmlにある小さなプログラムでより明確に示されています。

ここで、複雑な数学的分析を掘り下げることなく、シグマデルタADCの固有ノイズのレベルが非常に低い理由を理解してみましょう。

図に示すシグマデルタ変調器の構造図を考えてみましょう。 3、この形で想像してください(図6):

図 6.シグマ-デルタ変調器のブロック図

ここでは、コンパレータは連続した有用な信号と量子化ノイズを合計する加算器として表示されます。

積分器に伝達関数1 / sを持たせます。 次に、有用な信号をX(s)、シグマデルタ変調器の出力をY(s)、量子化ノイズをE(s)として提示すると、ADC伝達関数が得られます。

Y(s)= X(s)/(s + 1)+ E(s)s /(s + 1)

つまり、実際には、シグマ-デルタ変調器は、目的の信号のローパスフィルター(1 /(s + 1))とノイズのハイパスフィルター(s /(s + 1))であり、両方のフィルターは同じカットオフ周波数を持ちます。 スペクトルの高周波領域に集中したノイズは、変調器の後ろにあるデジタルローパスフィルターによって簡単に除去されます。

図 7.スペクトルの高周波部分のノイズを「混雑させる」現象

ただし、これはシグマデルタADCのノイズシェーピング現象の非常に簡略化された説明であることを理解してください。

したがって、シグマ-デルタADCの主な利点は、非常に低いレベルの固有ノイズによる高精度です。 ただし、高精度を実現するには、デジタルフィルターのカットオフ周波数を可能な限り低くする必要があります。これは、シグマデルタ変調器の周波数よりも何倍も低い値です。 したがって、シグマデルタADCの変換レートは低くなります。

オーディオ技術で使用できますが、主にセンサー信号を変換するための産業オートメーション、測定機器、および高精度が必要なその他のアプリケーションで使用されます。 しかし、高速は必要ありません。

ちょっとした歴史

歴史上最も古いADCへの言及は、おそらく、Paul M. Raineyの特許「ファクシミリ電信システム」、米国特許1,608,527、1921年7月20日出願、1926年11月30日発行です。 。

図 8. ADCの最初の特許

図 9. ADCダイレクトコンバージョン(1975)

図に示されているデバイスは、1975年に製造され、個別のコンパレータに基づいて組み立てられたComputer Labsによって製造された直接変換ADC MOD-4100です。 16個のコンパレータがあり(各コンパレータへの信号の伝播遅延を等しくするために半円に配置されています)、したがって、ADCの分解能は4ビットのみです。 変換速度100 MSPS、消費電力14ワット。

次の図は、直接変換ADCの高度なバージョンを示しています。

図 10. ADCダイレクトコンバージョン(1970)

Computer Labsが製造した1970 VHS-630には64個のコンパレータが含まれ、6ビット、30MSPSの速度、100ワットを消費しました(VHS-675の1975バージョンは75 MSPSの速度と130ワットの消費でした)。

文学

W.ケスター。 ADCアーキテクチャI:フラッシュコンバーター。 Analog Devices、MT-020チュートリアル。 www.analog.com/static/imported-files/tutorials/MT-020.pdf

W.ケスター。 ADCアーキテクチャII:逐次近似ADC。 Analog Devices、MT-021チュートリアル。 www.analog.com/static/imported-files/tutorials/MT-021.pdf

W.ケスター。 ADCアーキテクチャIII:シグマデルタADCの基本。 Analog Devices、MT-022チュートリアル。 www.analog.com/static/imported-files/tutorials/MT-022.pdf

W.ケスター。 ADCアーキテクチャIV:シグマデルタADCの高度な概念とアプリケーション。 Analog Devices、MT-023チュートリアル。 www.analog.com/static/imported-files/tutorials/MT-023.pdf